## **MP8030**

Fully Integrated, 802.3af/at/bt-Compliant PoE PD Interface with **High-Efficiency Flyback/Forward Controller**

#### DESCRIPTION

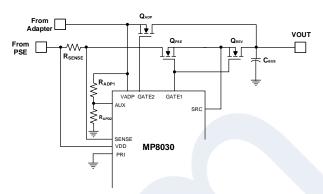

The MP8030 is a fully integrated, IEEE 802.3af/at/bt-compliant, Power over Ethernet (PoE), powered device (PD) power supply converter. The device features a PD interface and a high-efficiency flyback/forward controller.

The PD interface has all the functions of IEEE 802.3af/at/bt. It also integrates a 100V hot-swap MOSFET for ≤51W applications and one GATE1 driver to enhance efficiency for highpower applications (>51W). The GATE2 driver supports an external, low on resistance Nchannel MOSFET to prevent high power loss when the device is powered by an adapter.

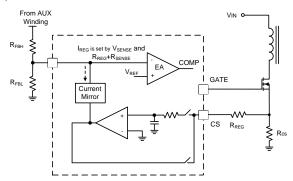

The flyback/forward controller is specifically designed for primary-side regulation (PSR) flyback applications, as well as secondary-side (SSR) active-clamp regulation forward applications. It also can be used in an SSR flyback topology.

The MP8030 features overload protection (OLP) with hiccup mode, short-circuit protection (SCP), over-voltage protection (OVP), and thermal shutdown.

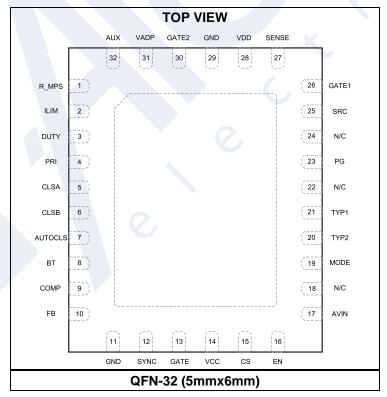

The MP8030 is available in a QFN-32 (5mmx6mm) package.

#### **FEATURES**

- Compliant with 802.3af/at/bt Specifications

- Internal Hot-Swap MOSFET for ≤51W Designs

- External FET with GATE1 for >51W Designs

- **GATE2 N-Channel MOSFET Driver for** Adapter Supply

- Supports Automatic Classification

- **Automatic Maintain Power Signature Function**

- Supports Flexible Topologies with DC/DC Design:

- Primary-Side Regulation (PSR) for Flyback Applications

- Secondary-Side Regulation (SSR) for Flyback Applications

- SSR for Active-Clamp Forward **Applications**

- **EMI** Reduction with Frequency Dithering

- Ethernet Alliance (EA Gen 2) Certified

- Available in a QFN-32 (5mmx6mm) Package

----- MPL

Optimized Performance with MPS Inductor MPL-AY Series

#### **APPLICATIONS**

- IEEE 802.3af/at/bt-Compliant Devices

- **Security Cameras**

- Video and VoIP Phones

- **WLAN Access Points**

- Internet of Things (IoT) Devices

- Pico Base Stations

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

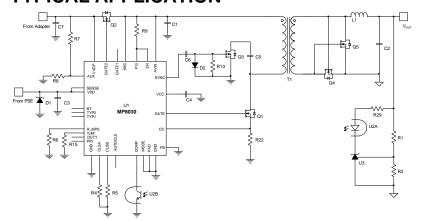

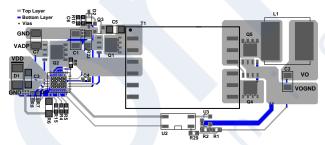

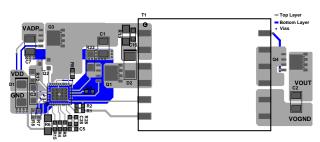

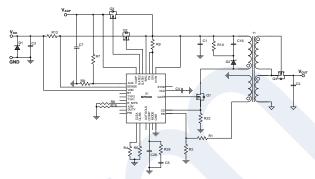

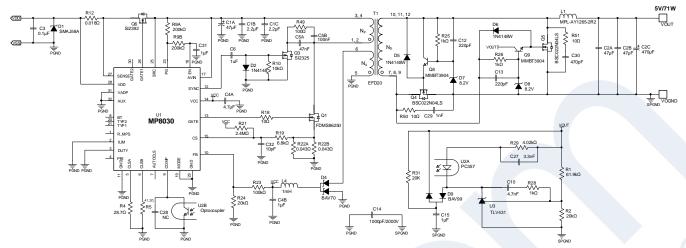

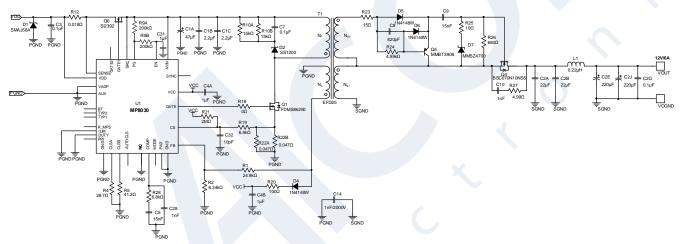

## **TYPICAL APPLICATION**

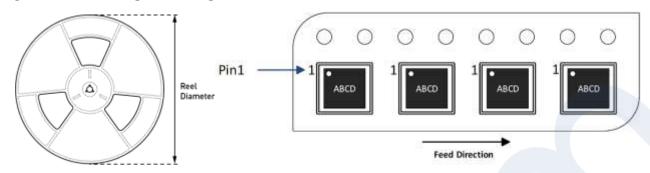

### ORDERING INFORMATION

| Part Number* | Package          | Top Marking | MSL Rating |

|--------------|------------------|-------------|------------|

| MP8030GQJ    | QFN-32 (5mmx6mm) | See Below   | 2          |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP8030GQJ-Z).

#### **TOP MARKING**

MPSYYWW MP8030 LLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP8030: Part number LLLLLL: Lot number

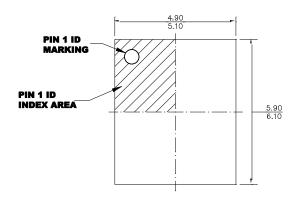

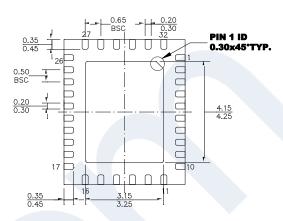

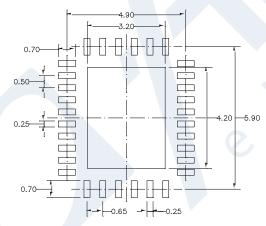

### **PACKAGE REFERENCE**

## **PIN FUNCTIONS**

| Pin#          | Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | R_MPS   | Automatically maintains power signature load resistor connection. The R_MPS pin generates a 24V output pulse when the maintain power signature function is triggered.                                                                                                                                                                                                                                                         |

| 2             | ILIM    | PD internal hot-swap MOSFET current limit configuration. See the Hot-Swap MOSFET and Current Limit section on page 26 for more details.                                                                                                                                                                                                                                                                                       |

| 3             | DUTY    | Automatic maintain power signature output duty setting pin. See the Automatic Maintain Power Signature Function section on page 28 for more details.                                                                                                                                                                                                                                                                          |

| 4             | PRI     | <b>PSE power and adapter power priority setting pin</b> . Internally pull PRI up to the internal 5V power source through a $1M\Omega$ resistor. The PSE power has a higher priority when PRI is low.                                                                                                                                                                                                                          |

| 5             | CLSA    | Power class signature pin. CLSA is used during the first two class events.                                                                                                                                                                                                                                                                                                                                                    |

| 6             | CLSB    | <b>Power class signature pin.</b> CLSB is used during the third class event and all subsequent class events.                                                                                                                                                                                                                                                                                                                  |

| 7             | AUTOCLS | Auto-class function enable pin. Pull AUTOCLS low to enable the auto-class function.                                                                                                                                                                                                                                                                                                                                           |

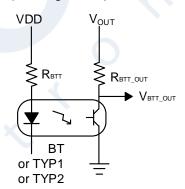

| 8             | BT      | PSE type indicator. BT is an open-drain output.                                                                                                                                                                                                                                                                                                                                                                               |

| 9             | COMP    | <b>DC/DC controller loop compensation pin</b> . COMP is the error amplifier (EA) output in PSR mode. COMP is internally pulled to 5V through a $10k\Omega$ resistor in SSR mode.                                                                                                                                                                                                                                              |

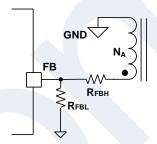

| 10            | FB      | <b>DC/DC controller output voltage feedback pin.</b> Connect one resistor divider from FB to the sensing winding to regulate the output voltage in PSR mode. In SSR mode, the internal EA is disabled. FB is only used to provide over-voltage protection (OVP).                                                                                                                                                              |

| 11, 29        | GND     | PD and DC/DC controller power ground. Pin 11 (GND) is the DC/DC controller's ground, and it is the GATE and SYNC drivers' return pin. Place the components related to the DC/DC controller close to pin 11. Pin 29 (GND) is the PD interface's ground. Place the components related to the PD close to pin 29. Connect pin 11 and pin 29 in the PCB. It is recommended to use an exposed thermal pad for thermal dissipation. |

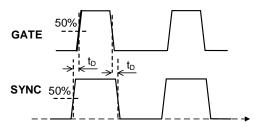

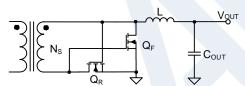

| 12            | SYNC    | The DC/DC controller's synchronous MOSFET gate driver pin.                                                                                                                                                                                                                                                                                                                                                                    |

| 13            | GATE    | The DC/DC controller's main MOSFET gate driver pin.                                                                                                                                                                                                                                                                                                                                                                           |

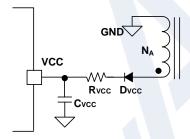

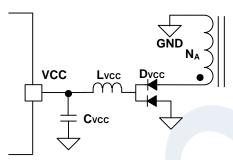

| 14            | VCC     | <b>DC/DC controller internal circuit supply pin.</b> VCC is powered through the internal LDO from AVIN. Connect a capacitor between this pin and GND to bypass the internal regulator. The VCC capacitor must be at minimum 1μF for flyback applications and at minimum 4.7μF for forward applications. VCC also can be powered from an external power source to reduce internal LDO loss.                                    |

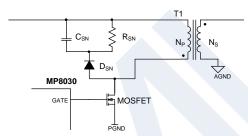

| 15            | CS      | <b>DC/DC controller current sense</b> , <b>PSR V</b> <sub>OUT</sub> <b>compensation</b> , <b>and frequency dither setting pin</b> . See the Frequency Dithering section on page 32 and the Output Voltage Compensation section on page 31 for more details.                                                                                                                                                                   |

| 16            | EN      | <b>DC/DC controller on/off control pin.</b> EN is internally connected to GND through a $2.5M\Omega$ resistor.                                                                                                                                                                                                                                                                                                                |

| 17            | AVIN    | <b>DC/DC controller input power supply pin.</b> Connect a bypass capacitor from the AVIN pin to GND. Connect AVIN to the SRC pin in application.                                                                                                                                                                                                                                                                              |

| 18,<br>22, 24 | NC      | No connection. It is recommended to connect these pins to the GND pin.                                                                                                                                                                                                                                                                                                                                                        |

| 19            | MODE    | <b>DC/DC controller PSR/SSR mode and dead-time setting pin.</b> See the Work Mode Detection section on page 30 for more details.                                                                                                                                                                                                                                                                                              |

|               | TYP2    | Allocated PSE power type indicator. TYP2 is an open-drain output.                                                                                                                                                                                                                                                                                                                                                             |

| 20            | TTPZ    | 7 modatod i oz powor typo maioatori i ii z io aii opon aram oatpat.                                                                                                                                                                                                                                                                                                                                                           |

4

## PIN FUNCTIONS (continued)

| Pin # | Name  | Description                                                                                                                                                                                                                                                          |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23    | PG    | <b>PD</b> power good indicator. Open-drain output, active high. PG enables the DC/DC controller.                                                                                                                                                                     |

| 25    | SRC   | <b>PD</b> hot-swap MOSFET source pin. It is the power output from the both internal and external hot-swap MOSFETs. Connect AVIN and the DC/DC power input to the SRC pin.                                                                                            |

| 26    | GATE1 | PD GATE driver of the external, parallel N-channel MOSFET for the PSE power supply.                                                                                                                                                                                  |

| 27    | SENSE | PD external MOSFET current-sense pin. Connect SENSE to VDD if this pin is not used.                                                                                                                                                                                  |

| 28    | VDD   | Positive power supply terminal from the PoE input power rail.                                                                                                                                                                                                        |

| 30    | GATE2 | PD GATE driver of the external N-channel MOSFET for the adapter power supply.                                                                                                                                                                                        |

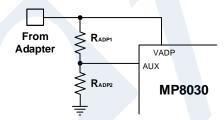

| 31    | VADP  | Positive power supply terminal from the adapter.                                                                                                                                                                                                                     |

| 32    | AUX   | Auxiliary power input detector pin. Use AUX to configure the adapter's auxiliary power under-voltage lockout (UVLO) threshold. AUX is internally pulled down to GND through a 2MΩ resistor. It is recommended to externally pull AUX to GND if this pin is not used. |

### **ABSOLUTE MAXIMUM RATINGS (1)** VDD, SENSE, SRC, TYP1, TYP2, PG, AUX, VADP, BT, AVIN .....-0.3V to +100V R MPS .....-0.3V to +30V VCC, GATE, SYNC.....-0.3V to +18V GATE1 to SRC .....-0.3V to +6.5V GATE2 to VADP .....-0.3V to +6.5V SENSE to VDD .....-6.5V to +0.3V FB .....-0.5V to +6.5V (2) All other pins .....-0.3V to +6.5V PG, TYP1, TYP2, BT sinking current....... 5mA EN sinking current ...... 0.5mA (3) FB sinking current ..... ±2mA (2) Continuous power dissipation ( $T_A = 25$ °C) (4) QFN-32 (5mmx6mm) ...... 3.9W (5) Junction temperature ......150°C Lead temperature ......260°C Storage temperature ..... -55°C to +150°C Recommended Operating Conditions (6) Supply voltage (V<sub>DD</sub>) ......0V to 57V Adapter supply voltage (V<sub>ADP</sub>)......0V to 57V VCC, GATE, SYNC voltage ...... 16V PG, TYP1, TYP2, BT max sink current...... 3mA EN maximum sink curent...... 0.4mA (3) FB maximum sink current..... ±1mA (2) Operating junction temp (T<sub>J</sub>).... -40°C to +125°C

| Thermal Resistance      | $oldsymbol{	heta}$ JA | $\boldsymbol{\theta}$ J $\boldsymbol{\theta}$ |      |

|-------------------------|-----------------------|-----------------------------------------------|------|

| QFN-32 (5mmx6mm)        |                       |                                               |      |

| EVL8030-QJ-00A (5)      | 32                    | .2                                            | °C/W |

| JESD51-7 <sup>(7)</sup> | 26                    | .1                                            | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- FB is clamped by an internal circuit. The sink/source current should be limited. See the Output Voltage Setting section on page 36 for more details.

- If EN is pulled above 6.5V externally, the pull-up current should be limited. Refer to Enable Control (EN) section on page 29 for more details.

- 4) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can produce an excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- Measured on EVL8030-QJ-00A, 4-layer, 1oz thick Cu, 160mmx55mm PCB.

- The device is not guaranteed to function outside of its operating conditions.

- 7) The value of θ<sub>JA</sub> given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

6

## **ELECTRICAL CHARACTERISTICS**

PD interface section,  $V_{DD}$  = 54V, SRC and AVIN are connected together,  $T_J$  = -40°C to +125°C (8), typical values are tested at  $T_J = 25$ °C, unless otherwise noted.

| Parameter                                              | Symbol                 | Condition                                                                                                            | Min  | Тур   | Max  | Units |

|--------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| Detection                                              |                        |                                                                                                                      |      |       |      |       |

| Detection on                                           | V <sub>DET-ON</sub>    | V <sub>DD</sub> rising                                                                                               |      | 1     | 1.4  | V     |

| Detection off                                          | V <sub>DET-OFF</sub>   | V <sub>DD</sub> rising                                                                                               | 10.1 | 11    |      | V     |

| Bias current                                           | I <sub>BIAS</sub>      | $V_{DD} = 10.1V$ , not in mark event, measure $I_{SUPPLY}$                                                           |      |       | 12   | μA    |

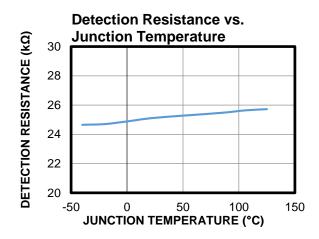

| Detection resistance                                   | R <sub>DET</sub>       | $V_{DD}$ = 1.5V to 10.1V, calculate with $\Delta V$ / $\Delta I$                                                     | 24.1 | 25    | 26.1 | kΩ    |

| Classification                                         |                        |                                                                                                                      |      |       |      |       |

| Classification stability time                          |                        | From V <sub>CL-ON</sub> to CLSA or CLSB, stable voltage output                                                       |      | 0.4   | 1    | ms    |

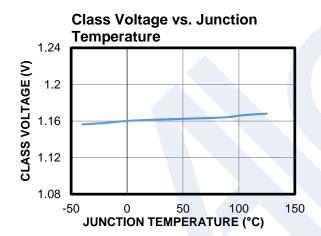

| V <sub>CLASS</sub> output voltage                      | V <sub>CLSA/B</sub>    | 13V < V <sub>DD</sub> < 21V, 1mA < I <sub>CLASS</sub> < 44mA                                                         | 1.11 | 1.16  | 1.21 | V     |

|                                                        |                        | $R_{CLASS} = 578\Omega$ , $13V \le V_{DD} \le 21V$ , measure input current, guaranteed by $V_{CLSA}$ and $V_{CLSB}$  | 1.8  | 2     | 2.4  |       |

|                                                        |                        | $R_{CLASS} = 110\Omega$ , $13V \le V_{DD} \le 21V$ , measure input current, guaranteed by $V_{CLSA}$ and $V_{CLSB}$  | 9.9  | 10.55 | 11.3 |       |

| Classification current for both the CLSA and CLSB pins | Iclass                 | $R_{CLASS} = 62\Omega$ , $13V \le V_{DD} \le 21V$ , measure input current, guaranteed by $V_{CLSA}$ and $V_{CLSB}$   | 17.7 | 18.7  | 19.8 | mA    |

|                                                        |                        | $R_{CLASS} = 41.2\Omega$ , $13V \le V_{DD} \le 21V$ , measure input current, guaranteed by $V_{CLSA}$ and $V_{CLSB}$ | 26.6 | 28.15 | 29.7 |       |

|                                                        |                        | $R_{CLASS} = 28.7\Omega$ , $13V \le V_{DD} \le 21V$ , measure input current, guaranteed by $V_{CLSA}$ and $V_{CLSB}$ | 38.2 | 40.4  | 42.6 |       |

| Auto-class signature current                           | I <sub>ACS</sub>       | After t <sub>ACS</sub> when the auto-class function is enabled, generated internally.                                | 1    |       | 3    | mA    |

| Auto-class signature timing                            | tacs                   | Change to I <sub>ACS</sub> , from triggering V <sub>CL-ON</sub>                                                      | 76   | 81.5  | 87   | ms    |

| Long first class event                                 | tLCE                   | Determine type 3/4 PoE, from triggering $V_{\text{CL-ON}}$                                                           | 76   | 81.5  | 87   | ms    |

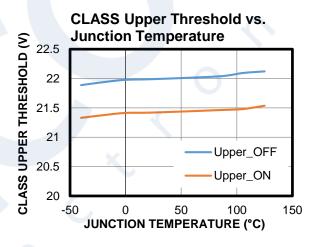

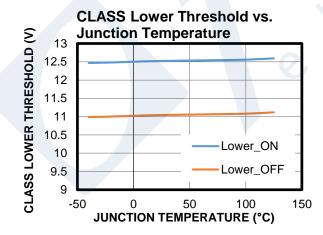

| Classification lower threshold                         | V <sub>CL-ON</sub>     | Regulator turns on, V <sub>DD</sub> rising                                                                           | 12   | 12.5  | 13   | V     |

| Classification lower threshold hysteresis              | V <sub>CL-L-HYS</sub>  | Low threshold hysteresis                                                                                             | 1.3  | 1.5   | 1.7  | V     |

| Classification upper threshold                         | V <sub>CL-OFF</sub>    | Regulator turns off, V <sub>DD</sub> rising                                                                          | 21   | 22    | 23   | V     |

| Classification upper threshold hysteresis              | V <sub>CL-H-H</sub> ys | High threshold hysteresis                                                                                            |      | 0.5   |      | V     |

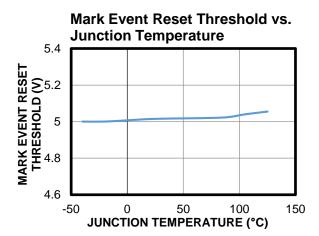

| Mark event reset threshold                             | Vmark-l                |                                                                                                                      | 4.5  | 5     | 5.5  | V     |

| Max mark event voltage                                 | V <sub>MARK-H</sub>    |                                                                                                                      | 10.5 | 11    | 11.5 | V     |

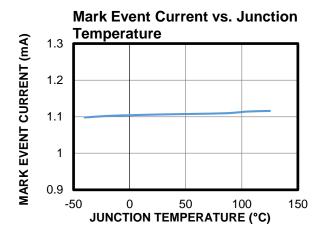

| Mark event current                                     | IMARK                  |                                                                                                                      | 0.5  | 1.1   | 2    | mA    |

PD interface section,  $V_{DD}$  = 54V, SRC and AVIN are connected together,  $T_J$  = -40°C to +125°C <sup>(8)</sup>, typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                               | Symbol               | Condition                                                                                                       | Min  | Тур  | Max  | Units               |

|-----------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|---------------------|

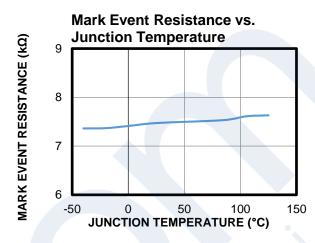

| Mark event resistance                   | RMARK                | 2-point measurement at 5.5V and 10.1V, with $\Delta V$ / $\Delta I$                                             |      |      | 12   | kΩ                  |

| IC supply current during classification | In-class             | V <sub>DD</sub> = 17.5V, CLSA and CLSB floating                                                                 |      | 180  | 300  | μA                  |

| Class leakage current                   | I <sub>LEAKAGE</sub> | V <sub>CLSA</sub> = V <sub>CLSB</sub> = 0V, V <sub>DD</sub> = 57V, test both the CLSA and CLSB pins             |      |      | 1    | μΑ                  |

| AUTOCLS low-voltage input               |                      |                                                                                                                 |      |      | 0.4  | V                   |

| AUTOCLS high-voltage input              |                      |                                                                                                                 | 1.2  |      |      | V                   |

| Under-Voltage Lockout (UV               | 'LO)                 |                                                                                                                 |      |      |      |                     |

| VDD turn-on threshold                   | $V_{\text{DD-R}}$    | V <sub>DD</sub> rising                                                                                          | 37   | 38.5 | 40   | V                   |

| VDD turn-off threshold                  | V <sub>DD-F</sub>    | V <sub>DD</sub> falling                                                                                         | 30   | 31.5 | 33   | V                   |

| VDD UVLO hysteresis                     | V <sub>DD-HYS</sub>  |                                                                                                                 | 5    | 7    |      | V                   |

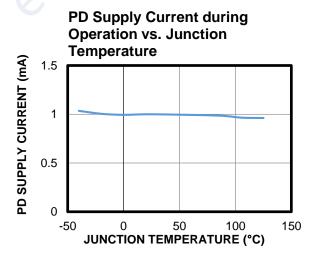

| IC supply current during operation      | lin                  | No load and no R_MPS resistor, disconnect AVIN from SRC                                                         |      | 1    | 1.5  | mA                  |

| Input leakage current                   |                      | V <sub>DD</sub> = 29.5V                                                                                         |      | 150  | 250  | μΑ                  |

| Hot-Swap MOSFET and Cur                 | rrent Limit          |                                                                                                                 |      |      |      |                     |

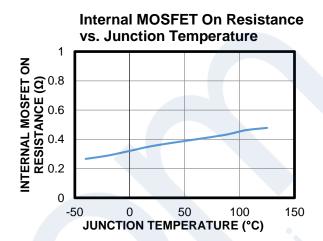

| Internal MOSFET on resistance           | Ron                  | I <sub>SRC</sub> = 500mA                                                                                        |      | 0.35 |      | Ω                   |

| Leakage current                         | I <sub>SRC-LK</sub>  | V <sub>DD</sub> = 57V, V <sub>SRC</sub> = 0V, AUX = high, PRI = high                                            | 1    | 1    | 15   | μA                  |

| ILIM pin detection period               |                      |                                                                                                                 |      | 270  |      | μs                  |

| ILIM pin detection current              |                      |                                                                                                                 | 130  | 165  | 180  | μΑ                  |

| II IM nin valtana thuadhald             |                      | 0.9A setting voltage range                                                                                      |      |      | 0.8  | V                   |

| ILIM pin voltage threshold              |                      | 1.6A setting voltage range                                                                                      | 1    |      | 2.2  | V                   |

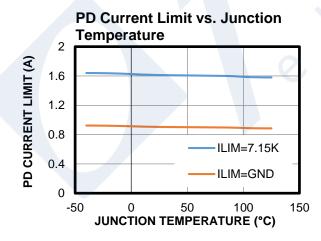

| Internal MOSFET current                 |                      | $ILIM = 0V$ , $V_{SRC}$ drops from VDD, $V_{DD}$ - $V_{SRC} = 1V$                                               | 0.75 | 0.9  | 1.05 | А                   |

| limit                                   | Ішміт                | ILIM connected to GND through a $7.15kΩ$ resistor, $V_{SRC}$ drops from VDD, $V_{DD}$ - $V_{SRC}$ = 1V          | 1.4  | 1.6  | 1.8  | А                   |

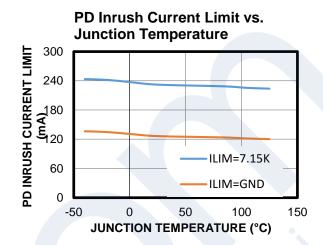

| Internal MOSFET inrush                  |                      | ILIM = 0V, $V_{SRC}$ ramps up from low to high, $V_{DD}$ - $V_{SRC}$ = 1V                                       | 70   | 130  | 190  | mA                  |

| limit                                   | Inrush               | ILIM connected to GND through a 7.15kΩ resistor. $V_{SRC}$ ramps up from low to high, $V_{DD}$ - $V_{SRC}$ = 1V | 170  | 230  | 290  | mA                  |

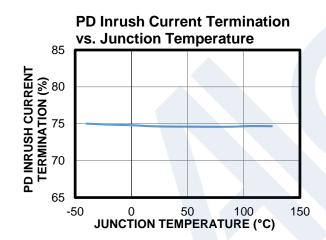

| Inrush current termination              | I <sub>TERM</sub>    | V <sub>SRC</sub> rising, I <sub>TERM</sub> / I <sub>INRUSH</sub>                                                |      | 75%  |      | I <sub>INRUSH</sub> |

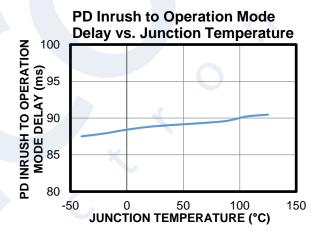

| Inrush to operation mode delay          | t <sub>DELAY</sub>   |                                                                                                                 | 80   | 90   | 100  | ms                  |

| Current foldback threshold              |                      | V <sub>SRC</sub> falling, V <sub>DD</sub> - V <sub>SRC</sub>                                                    | 8.2  | 10   | 11.8 | V                   |

| Foldback deglitch time (9)              |                      | V <sub>SRC</sub> falling to inrush current foldback                                                             |      | 1    |      | ms                  |

| GATE1 source current                    |                      | V <sub>GATE1</sub> - V <sub>SRC</sub> = 4V                                                                      |      | 10   |      | μA                  |

| GATE1 sink current                      |                      | V <sub>GATE1</sub> - V <sub>SRC</sub> = 4V                                                                      |      | 30   |      | μA                  |

PD interface section,  $V_{DD}$  = 54V, SRC and AVIN are connected together,  $T_J$  = -40°C to +125°C <sup>(8)</sup>, typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                                       | Symbol                | Condition                                                          | Min | Тур   | Max | Units |

|-----------------------------------------------------------------|-----------------------|--------------------------------------------------------------------|-----|-------|-----|-------|

| GATE1 max driving voltage                                       |                       |                                                                    |     | 6     |     | V     |

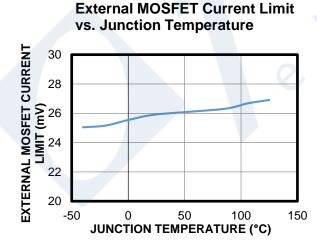

| External MOSFET current limit                                   |                       | V <sub>DD</sub> - V <sub>SENSE</sub>                               | 22  | 26    | 30  | mV    |

| SENSE pin leakage current                                       |                       | V <sub>SENSE</sub> = V <sub>DD</sub> = 54V                         |     |       | 0.1 | μA    |

| PG, BT, TYP1, TYP2                                              |                       |                                                                    |     |       |     |       |

| Output low voltage                                              |                       | Isink = 1mA                                                        |     | 0.2   | 0.4 | V     |

| Leakage current                                                 |                       | Logic = high, connect to 57V                                       |     |       | 1   | μΑ    |

| Maintain Power Signature                                        |                       |                                                                    |     |       |     |       |

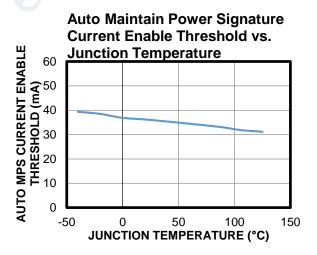

| Automatic maintain power signature current enable threshold     | I <sub>PORT-MPS</sub> | Load current falling                                               |     | 36    |     | mA    |

| Automatic maintain power signature current threshold hysteresis |                       | Load current rises to disable the maintain power signature current |     | 10    |     | mA    |

| R_MPS pin output voltage                                        |                       | 1mA to 20mA                                                        | 23  | 24    | 25  | V     |

| Type 1/2 DOE D MDC                                              |                       | Duty cycle                                                         |     | 37%   |     |       |

| Type 1/2 PSE, R_MPS output duty cycle                           |                       | On period                                                          | 75  | 85    | 95  | ms    |

| output duty by old                                              |                       | Off period                                                         | 115 | 140   | 165 | ms    |

| Type 3/4 PSE, R_MPS                                             |                       | Duty cycle                                                         |     | 6%    |     |       |

| output duty cycle with DUTY                                     |                       | On period                                                          | 14  | 16    | 18  | ms    |

| pin shorted to GND                                              |                       | Off period                                                         | 210 | 250   | 290 | ms    |

| Type 3/4 PSE, R_MPS                                             |                       | Duty cycle                                                         |     | 11.5% |     | ms    |

| output duty cycle with DUTY pin to GND through a                |                       | On period                                                          | 26  | 31    | 36  | ms    |

| 7.15kΩ resistor                                                 |                       | Off period                                                         | 200 | 235   | 270 | ms    |

| Type 3/4 PSE, R_MPS                                             |                       | Duty cycle                                                         |     | 17%   |     |       |

| output duty cycle with DUTY                                     |                       | On period                                                          | 39  | 45    | 52  | ms    |

| pin floating                                                    |                       | Off period                                                         | 190 | 221   | 260 | ms    |

| External FET voltage drop control threshold                     |                       | V <sub>DS</sub> = V <sub>SENSE</sub> - V <sub>SRC</sub>            |     | 26    |     | mV    |

| DUTY pin detection current                                      |                       |                                                                    | 130 | 165   | 180 | μΑ    |

| DUTY pin detection period                                       |                       | 0,                                                                 |     | 130   |     | μs    |

|                                                                 |                       | 6% duty cycle setting voltage range                                |     |       | 0.8 | V     |

| DUTY pin voltage threshold                                      |                       | 11.5% duty cycle setting voltage range                             | 1   |       | 2.2 | V     |

|                                                                 |                       | 17% duty cycle setting voltage range                               | 2.5 |       |     | V     |

| Adapter Supply                                                  |                       |                                                                    |     |       |     |       |

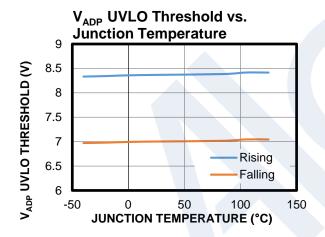

| VADP pin UVLO rising                                            | ADP <sub>UV-R</sub>   |                                                                    | 7.8 | 8.3   | 8.8 | V     |

| VADP pin UVLO falling                                           | ADP <sub>UV-F</sub>   |                                                                    | 6.5 | 7     | 7.5 | V     |

9

PD interface section,  $V_{DD}$  = 54V, SRC and AVIN are connected together,  $T_J$  = -40°C to +125°C  $^{(8)}$ , typical values are tested at T<sub>J</sub> = 25°C, unless otherwise noted.

| Parameter                         | Symbol               | Condition                                                                       | Min  | Тур  | Max  | Units |

|-----------------------------------|----------------------|---------------------------------------------------------------------------------|------|------|------|-------|

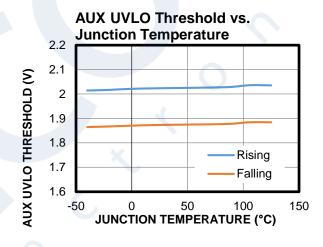

| AUX pin high threshold voltage    | V <sub>AUX-H</sub>   |                                                                                 | 1.92 | 2    | 2.08 | V     |

| AUX pin threshold hysteresis      | V <sub>AUX-HYS</sub> |                                                                                 |      | 0.15 |      | V     |

| ALIV lookaga aurrant              |                      | V <sub>AUX</sub> = 2V                                                           |      | 1    |      | μΑ    |

| AUX leakage current               |                      | V <sub>AUX</sub> = 57V                                                          |      | 2.5  |      | μΑ    |

| GATE2 source current              |                      | VGATE2 - VADP = 4V                                                              |      | 20   |      | μΑ    |

| GATE2 sink current                |                      | VGATE2 - VADP = 4V                                                              | 200  |      |      | μΑ    |

| GATE2 max driving voltage         |                      | GATE2 to VADP                                                                   |      | 6    |      | V     |

| GATE2 turn-on threshold           |                      | V <sub>ADP</sub> - V <sub>SRC</sub> voltage after the adapter supply is enabled | 0    |      | 0.45 | V     |

| Power Priority                    |                      |                                                                                 |      |      |      | •     |

| PRI pin input high voltage        |                      |                                                                                 | 2    |      |      | V     |

| PRI pin input low voltage         |                      |                                                                                 |      |      | 0.4  | V     |

| PRI pin internal pull up resistor |                      | Pull up to the internal 5V V <sub>CC</sub>                                      |      | 1    |      | МΩ    |

| Thermal Shutdown                  |                      |                                                                                 |      |      |      |       |

| Thermal shutdown temperature (9)  | T <sub>PD-SD</sub>   |                                                                                 |      | 150  |      | °C    |

| Thermal shutdown hysteresis (9)   | T <sub>PD-HYS</sub>  |                                                                                 | 4    | 20   |      | °C    |

## **ELECTRICAL CHARACTERISTICS**

Controller section,  $V_{DD}$  = 54V, SRC and AVIN are connected together,  $T_J$  = -40°C to +125°C  $^{(8)}$ , typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                   | Symbol              | Condition                                                                                                                                                                                                                                                                       | Min      | Тур  | Max      | Units     |

|---------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|----------|-----------|

| Power Supply and UVLO                       |                     |                                                                                                                                                                                                                                                                                 |          |      | •        |           |

| AVIN UVLO rising threshold                  | V <sub>AVIN-R</sub> | V <sub>AVIN</sub> rising, start charging to V <sub>CC</sub>                                                                                                                                                                                                                     | 4.5      | 5.5  | 6.5      | V         |

| AVIN UVLO falling threshold                 | V <sub>AVIN-F</sub> | V <sub>AVIN</sub> falling                                                                                                                                                                                                                                                       | 3.8      | 4.8  | 5.8      | V         |

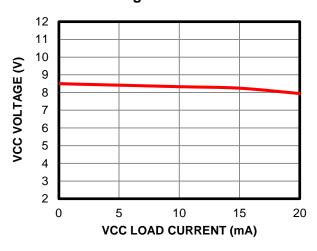

| VCC regulation voltage                      | Vcc                 | Load = 0mA to 20mA                                                                                                                                                                                                                                                              |          | 8.5  |          | V         |

| VCC dropout voltage                         | Vcc-drop            | V <sub>AVIN</sub> = 8V, I <sub>VCC</sub> = 10mA                                                                                                                                                                                                                                 |          | 1.5  |          | V         |

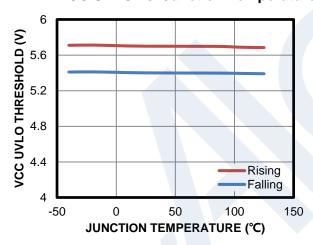

| VCC UVLO rising threshold                   | V <sub>CC-R</sub>   | Vavin > Vavin-R, Vcc rising                                                                                                                                                                                                                                                     | 5.4      | 5.7  | 6.0      | V         |

| VCC UVLO falling threshold                  | V <sub>CC-F</sub>   | V <sub>AVIN</sub> > V <sub>AVIN-R</sub> , V <sub>CC</sub> falling                                                                                                                                                                                                               | 5        | 5.3  | 5.6      | V         |

| Quiescent current                           | Ια                  | MODE pin float, $V_{FB}$ = -0.1V, CS = 100mV, COMP = 0V, $I_Q$ = $I_{DD}$ - $I_{COMP}$ , GATE and SYNC floating, test AVIN pin                                                                                                                                                  |          | 900  |          | μA        |

|                                             |                     | $\label{eq:MODE} \begin{array}{l} \text{MODE} = \text{OV}, \ \text{V}_{\text{COMP}} = \text{OV}, \ \text{I}_{\text{Q}} = \text{I}_{\text{DD}} - \\ \text{I}_{\text{COMP}}, \ \text{GATE} \ \text{and} \ \text{SYNC} \ \text{floating}, \\ \text{test the AVIN pin} \end{array}$ |          | 500  |          | μΑ        |

| Enable (EN) Control                         |                     |                                                                                                                                                                                                                                                                                 |          |      | _        |           |

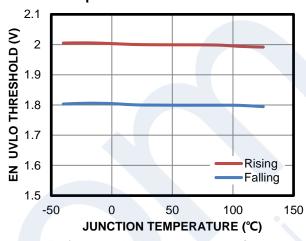

| EN turn-on threshold                        | $V_{EN-R}$          | Start switching                                                                                                                                                                                                                                                                 | 1.9      | 2    | 2.1      | V         |

| EN turn-on hysteresis                       | V <sub>EN-HYS</sub> | Stop switching                                                                                                                                                                                                                                                                  |          | 0.2  |          | V         |

| EN high micro-power threshold               | V <sub>EN-H</sub>   | Start internal logic                                                                                                                                                                                                                                                            |          | O    | 1.0      | V         |

| EN low micro-power threshold                | V <sub>EN-L</sub>   | Stop internal logic                                                                                                                                                                                                                                                             | 0.4      |      |          | V         |

| EN input current                            | I <sub>EN</sub>     | $V_{EN} = 5V$                                                                                                                                                                                                                                                                   |          | 2    |          | μA        |

| EN turn-on delay                            |                     | EN on to GATE output                                                                                                                                                                                                                                                            | <b>-</b> | 500  |          | μs        |

| Voltage Feedback (FB)                       |                     |                                                                                                                                                                                                                                                                                 |          |      |          |           |

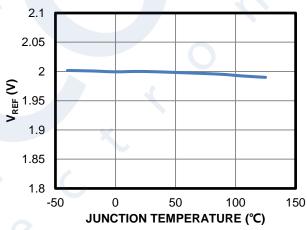

| FB reference voltage                        | $V_{REF}$           | $T_J = 25^{\circ}C$                                                                                                                                                                                                                                                             | 1.98     | 2    | 2.02     | V         |

| rb reference voltage                        | VREF                | $T_J = -40$ °C to $+125$ °C                                                                                                                                                                                                                                                     | 1.97     | 2    | 2.03     | V         |

| FB leakage current                          | I <sub>FB</sub>     | V <sub>FB</sub> = 2V                                                                                                                                                                                                                                                            |          | 10   | 50       | nA        |

| FB OVP threshold                            | $V_{FBOVP}$         |                                                                                                                                                                                                                                                                                 | 120%     | 125% | 130%     | $V_{REF}$ |

| OVP hiccup off time                         |                     |                                                                                                                                                                                                                                                                                 |          | 340  |          | ms        |

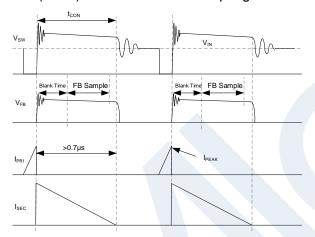

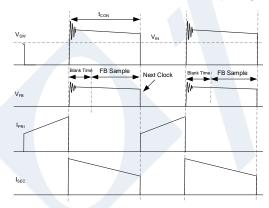

| Minimum diode conduction time for FB sample | <b>t</b> SAMPLE     |                                                                                                                                                                                                                                                                                 |          | 0.5  | 0.6 (10) | μs        |

|                                             |                     | $V_{CS} = 50 \text{mV}, R_{CS-GND} = 3.3 \text{k}\Omega^{(11)}$                                                                                                                                                                                                                 |          | 2.7  |          | μΑ        |

| Regulation compensation current into FB     |                     | $V_{CS} = 50 \text{mV}, R_{CS-GND} = 6.8 \text{k}\Omega^{(11)}$                                                                                                                                                                                                                 |          | 5.4  |          | μΑ        |

| odirent into 1 B                            |                     | $V_{CS} = 50 \text{mV}, R_{CS-GND} = 12.7 \text{k}\Omega^{(11)}$                                                                                                                                                                                                                |          | 10.8 |          | μΑ        |

| Error Amplifier (EA)                        | V                   |                                                                                                                                                                                                                                                                                 |          |      |          |           |

| EA transconductance                         | G <sub>EA</sub>     | MODE floating, $V_{FB}$ is $\pm 50 mV$ from $V_{REF}$ , $V_{COMP} = 1.5V$                                                                                                                                                                                                       |          | 0.59 |          | mA/V      |

| EA maximum source current                   | I <sub>EA</sub>     | MODE floating, $V_{COMP} = 1.5V$ , $V_{FB} = 1.9V$                                                                                                                                                                                                                              |          | -110 |          | μA        |

Controller section,  $V_{DD}$  = 54V, SRC and AVIN are connected together,  $T_J$  = -40°C to +125°C <sup>(8)</sup>, typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                     | Symbol                                 | Condition                                                          | Min  | Тур | Max  | Units |

|-----------------------------------------------|----------------------------------------|--------------------------------------------------------------------|------|-----|------|-------|

| EA maximum sink current                       | I <sub>EA</sub>                        | MODE floating, V <sub>COMP</sub> = 1.5V,<br>V <sub>FB</sub> = 2.1V |      | 110 |      | μA    |

| COMP bink waltana                             | \ /                                    | MODE floating, V <sub>FB</sub> = 1.9V                              |      | 4   |      | .,    |

| COMP high voltage                             | $V_{COMP}$                             | MODE = 0V, float COMP                                              |      | 5   |      | V     |

| COMP internal pull-up resistor                |                                        | SSR mode                                                           |      | 10  |      | kΩ    |

| Soft Start (SS)                               |                                        |                                                                    |      |     |      |       |

| Internal soft-start time                      | tss                                    | MODE floating, test FB from 0V to 2V                               |      | 15  |      | ms    |

|                                               |                                        | MODE = 0V, test COMP from 1.5V to 3.5V                             |      | 20  |      | 0     |

| Current Sense (CS)                            |                                        |                                                                    |      |     |      | •     |

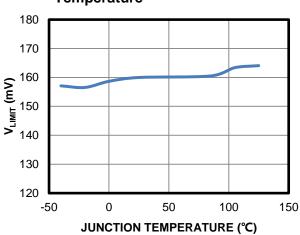

| Maximum CS limit                              | ILIMIT-MAX                             |                                                                    | 140  | 160 | 180  | mV    |

| Low threshold current limit                   | ILIMIT-MIN                             | In PSR mode                                                        | 33   | 36  | 39   | mV    |

| SCP limit                                     |                                        |                                                                    | 240  | 300 | 360  | mV    |

| Current leading edge blanking time            | tLEB                                   |                                                                    |      | 250 |      | ns    |

| CS amplifier gain                             | Gcs                                    |                                                                    |      | 11  |      | V/V   |

| CS input bias current                         |                                        | V <sub>CS</sub> = 160mV                                            |      | 10  | 50   | nA    |

| Pulse-Width Modulation (PV                    | VM) Switc                              | hing                                                               | 1    |     |      |       |

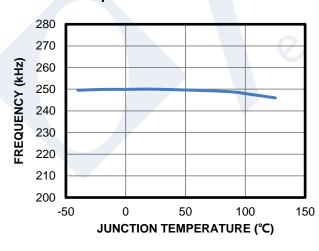

| Switching frequency                           | fsw                                    |                                                                    | 225  | 250 | 275  | kHz   |

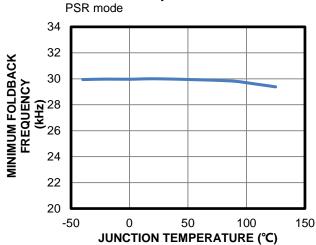

| Minimum foldback frequency in PFM mode        |                                        | In PSR mode, COMP = 0V                                             |      | 30  |      | kHz   |

| Mode, Dead Time, Dither, Vo                   | оит Сотре                              | ensation Setting (MODE and CS Pi                                   | n)   |     |      |       |

| MODE pin detection current                    | I <sub>MODE</sub>                      |                                                                    | 35   | 40  | 45   | μΑ    |

| CS pin detection current                      | Ics                                    |                                                                    | 90   | 100 | 110  | μΑ    |

| MODE and CS pin detection period              | t <sub>MODE</sub> ,                    |                                                                    |      | 200 |      | μs    |

|                                               |                                        | Voltage level 1 range                                              |      |     | 0.15 | V     |

| MODE OO : I day                               |                                        | Voltage level 2 range                                              | 0.25 |     | 0.4  | V     |

| MODE, CS pin detection threshold voltage (12) | V <sub>MODE</sub> ,<br>V <sub>CS</sub> | Voltage level 3 range                                              | 0.55 |     | 0.85 | V     |

| unconoid voltage                              | VCS                                    | Voltage level 4 range                                              | 1.1  |     | 1.5  | V     |

|                                               |                                        | Voltage level 5 range                                              | 2.2  |     |      | V     |

| <b>GATE Driver Signal</b>                     |                                        |                                                                    |      |     |      |       |

| GATE driver impedance (sourcing)              | I <sub>GATE</sub>                      | I <sub>GATE</sub> = -20mA                                          |      | 2   |      | Ω     |

| GATE driver impedance (sinking)               | I <sub>GATE</sub>                      | I <sub>GATE</sub> = 20mA                                           |      | 1.7 |      | Ω     |

| GATE source current capability <sup>(9)</sup> |                                        | Vcc = 8.5V, GATE = 10nF, test gate rising speed                    |      | 2   |      | А     |

Controller section,  $V_{DD}$  = 54V, SRC and AVIN are connected together,  $T_J$  = -40°C to +125°C (8), typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                          | Symbol            | Condition                                            | Min                    | Тур | Max  | Units       |

|----------------------------------------------------|-------------------|------------------------------------------------------|------------------------|-----|------|-------------|

| GATE sink current capability (9)                   |                   | Vcc = 8.5V, GATE = 10nF, test gate falling speed     |                        | 1.7 |      | Α           |

| GATE output high voltage                           | V <sub>GATE</sub> |                                                      | V <sub>CC</sub> - 0.05 |     |      | V           |

| GATE output low voltage                            | V <sub>GATE</sub> |                                                      |                        |     | 0.05 | <b>&gt;</b> |

| Minimum GATE on time                               | ton-min           |                                                      |                        | 250 |      | ns          |

| GATE max duty cycle                                | D <sub>MAX</sub>  |                                                      |                        | 70  |      | %           |

| SYNC Driver Signal                                 |                   |                                                      |                        |     |      |             |

| SYNC driver impedance (sourcing)                   | Isync             | I <sub>GATE</sub> = -20mA                            |                        | 5   |      | Ω           |

| SYNC driver impedance (sinking)                    | I <sub>SYNC</sub> | I <sub>GATE</sub> = 20mA                             |                        | 2.3 |      | Ω           |

| SYNC source current capability <sup>(9)</sup>      |                   | Vcc = 8.5V, SYNC = 10nF, test the SYNC rising speed  |                        | 0.8 |      | А           |

| SYNC sink current capability                       |                   | Vcc = 8.5V, SYNC = 10nF, test the SYNC falling speed |                        | 1.2 | 0    | Α           |

| SYNC output high voltage                           | Vsync             |                                                      | V <sub>CC</sub> - 0.05 |     |      | V           |

| SYNC output low voltage                            | Vsync             |                                                      |                        |     | 0.05 | V           |

| Protection                                         |                   |                                                      | 1                      |     |      |             |

| Overload protection hiccup on time <sup>(9)</sup>  |                   |                                                      |                        | 4.8 |      | ms          |

| Overload protection hiccup off time <sup>(9)</sup> |                   |                                                      |                        | 340 |      | ms          |

| Thermal shutdown temperature <sup>(9)</sup>        | T <sub>SD</sub>   |                                                      |                        | 150 |      | °C          |

| Thermal shutdown hysteresis (9)                    | T <sub>H</sub> ys | 0.                                                   |                        | 20  |      | °C          |

#### Notes:

- 8) Guaranteed by over-temperature correlation. Not tested in production.

- 9) Guaranteed by characterization. Not tested in production.

- 10) It is recommended to make the output diode conduction time longer than 0.7µs.

- 11) R<sub>CS-GND</sub> is the resistance from the CS pin to GND. This includes the current-sense resistor from the MOSFET source to GND and the resistor from the MOSFET's source to the CS pin.

- 12) For different voltage levels, see Table 6 on page 30 and Table 7 on page 32.

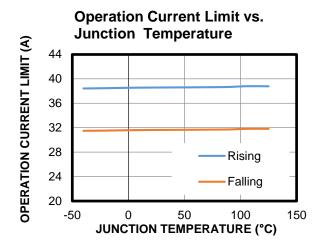

### TYPICAL CHARACTERISTICS

VDD = 54V,  $T_A = 25$ °C, unless otherwise noted.

$V_{DD} = 54V$ ,  $T_A = 25$ °C, unless otherwise noted.

$V_{DD} = 54V$ ,  $T_A = 25$ °C, unless otherwise noted.

$V_{DD} = 54V$ ,  $T_A = 25$ °C, unless otherwise noted.

#### VCC Voltage vs. VCC Load Current

#### VCC UVLO vs. Junction Temperature

## Frequency vs. Junction Temperature

## **EN UVLO Threshold vs. Junction Temperature**

# Reference Voltage vs. Junction Temperature

# Minimum Foldback Frequency vs. Junction Temperature

$V_{DD} = 54V$ ,  $T_A = 25$ °C, unless otherwise noted.

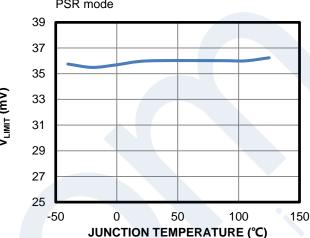

#### **Current Limit vs. Junction Temperature**

#### Low Threshold Current Limit vs. **Junction Temperature** PSR mode

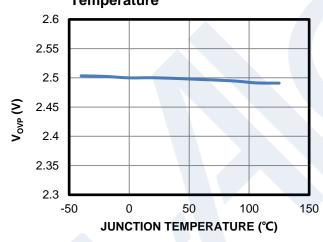

## **OVP Threshold vs. Junction Temperature**

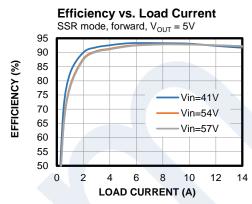

#### TYPICAL PERFORMANCE CHARACTERISTICS

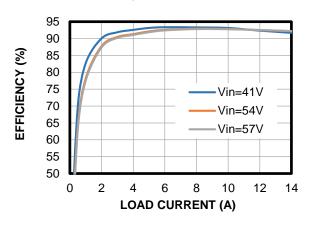

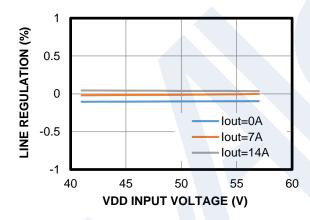

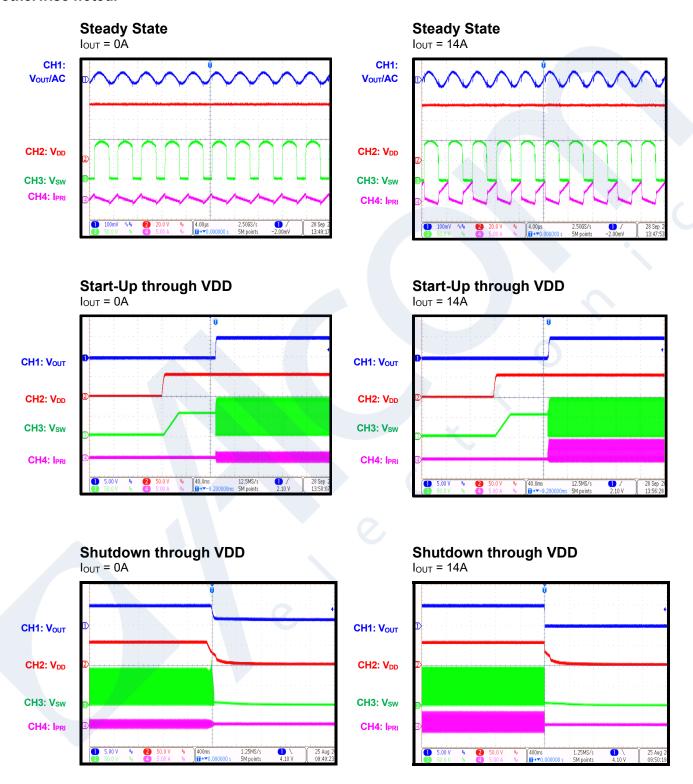

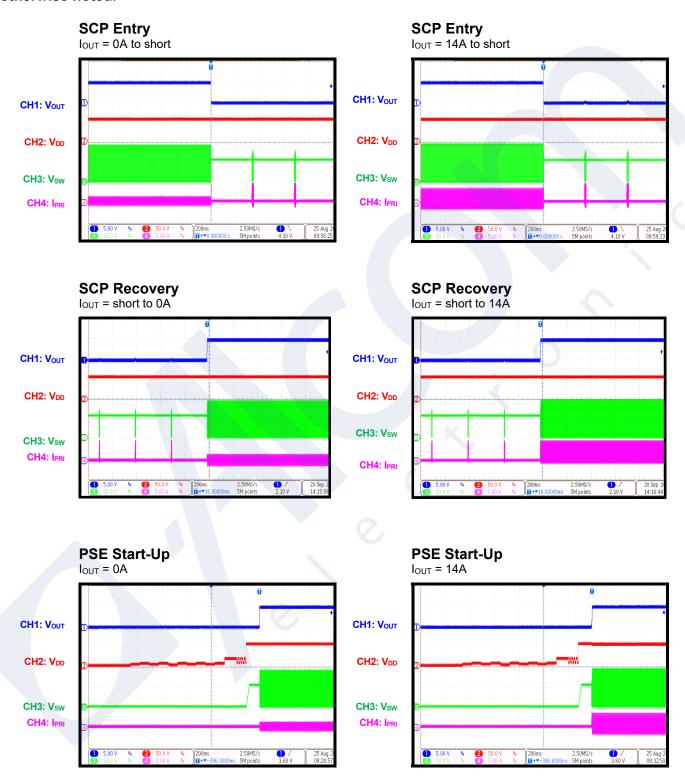

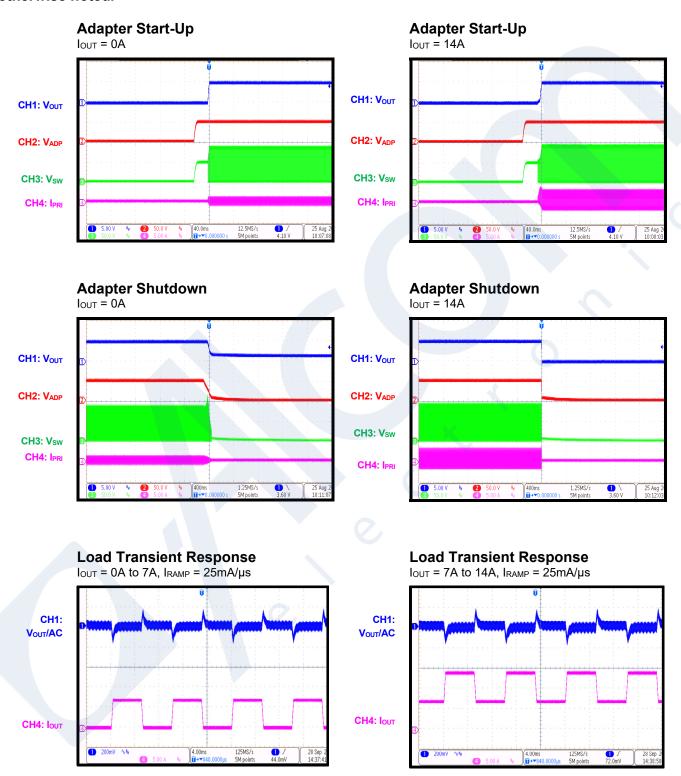

$V_{DD}$  = 54V,  $V_{ADP}$  = 48V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 14A,  $T_A$  = 25°C, set in SSR forward mode, unless otherwise noted.

#### **Efficiency vs. Load Current**

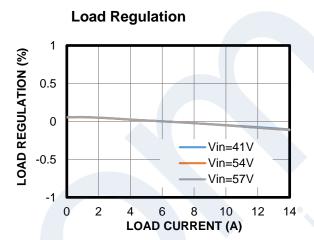

#### **Line Regulation**

$V_{DD}$  = 54V,  $V_{ADP}$  = 48V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 14A,  $T_A$  = 25°C, set in SSR forward mode, unless otherwise noted.

$V_{DD}$  = 54V,  $V_{ADP}$  = 48V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 14A,  $T_A$  = 25°C, set in SSR forward mode, unless otherwise noted.

21

$V_{DD}$  = 54V,  $V_{ADP}$  = 48V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 14A,  $T_A$  = 25°C, set in SSR forward mode, unless otherwise noted.

$V_{DD}$  = 54V,  $V_{ADP}$  = 48V,  $V_{OUT}$  = 5V,  $I_{OUT}$  = 14A,  $T_A$  = 25°C, set in SSR forward mode, unless otherwise noted.

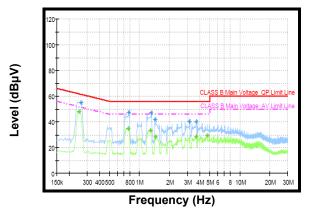

#### **Conducted Emissions Results**

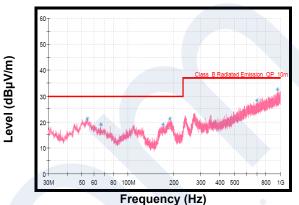

#### **Radiated Emissions Results**

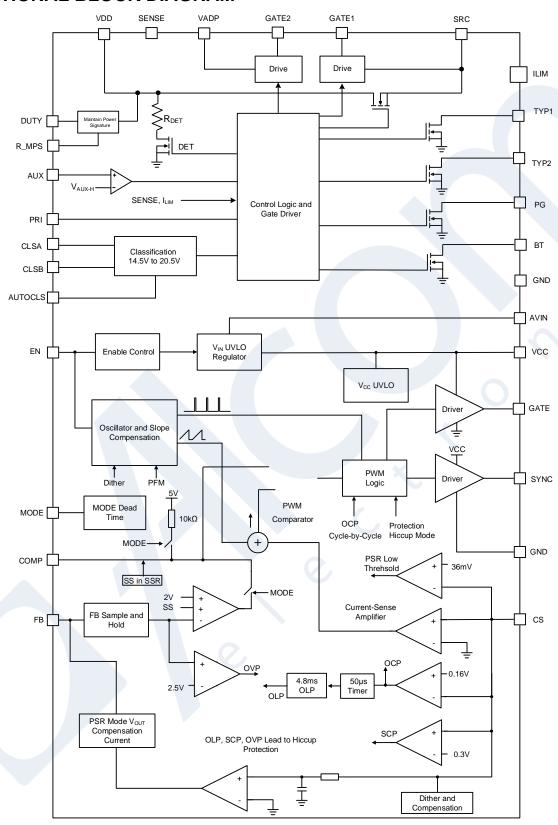

### **FUNCTIONAL BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

#### **OPERATION**

The MP8030 is a fully integrated, IEEE 802.3af/at/bt-compliant, Power over Ethernet (PoE) powered device (PD) power supply converter. It includes a PD interface and high-efficiency flyback/forward controller.

#### PD INTERFACE

The MP8030 PD interface has all the functions of IEEE 802.3af/at/bt, including detection, classification, input current control, a 100V hotswap MOSFET, and an automatic maintain power signature function.

#### **Detection**

The MP8030 PD integrates an internal detection resistor. When the PSE applies two safe voltages (between 2.7V and 10.1V) to the MP8030, the MP8030 PD will typically shows a  $25k\Omega$  resistance between the VDD and GND pins.

#### Classification

PSE distributes power to PDs based on the classification results. Classification mode is active when the input voltage is between 14.5V and 20.5V. The MP8030 PD presents different currents in classification mode (see Table 1).

|             |                     |                               |                   | _                 | _                    |                      |

|-------------|---------------------|-------------------------------|-------------------|-------------------|----------------------|----------------------|

| PD<br>Class | Power<br>Rating (W) | Class Cycle with<br>Max Power | CLSA<br>Signature | CLSB<br>Signature | CLSA<br>Resistor (Ω) | CLSB<br>Resistor (Ω) |

| 0           | 0.44 to 12.95       | 1                             | 0                 | 0                 | 578                  | 578                  |

| 1           | 0.44 to 3.84        | 1                             | 1                 | 1                 | 110                  | 110                  |

| 2           | 3.84 to 6.49        | 1                             | 2                 | 2                 | 62                   | 62                   |

| 3           | 6.49 to 12.95       | 1                             | 3                 | 3                 | 41.2                 | 41.2                 |

| 4           | 12.95 to 25.5       | 2, 3                          | 4                 | 4                 | 28.7                 | 28.7                 |

| 5           | 25.5 to 40          | 4                             | 4                 | 0                 | 28.7                 | 578                  |

| 6           | 40 to 51            | 4                             | 4                 | 1                 | 28.7                 | 110                  |

| 7           | 51 to 62            | 5                             | 4                 | 2                 | 28.7                 | 62                   |

| 8           | 62 to 71.3          | 5                             | 4                 | 3                 | 28.7                 | 41.2                 |

Table 1: Different Classification Power Rating and Setting with PD

IEEE802.3bt supports an 8-level class power rating, with up to 5 classification cycle operations. These classification cycles have the below functions:

- All PSEs perform one cycle classification for the class 0, class 1, class 2, and class 3 PDs.

- Type 2 PSEs perform 2-cycle classification if a class 4 signature is detected during the first class cycle.

- Type 3 and type 4 PSEs start their third cycle classification if a class 4 signature is detected during the first and second class cycle. Based on the third classification result, type 3 and type 4 PSEs follow one of the operations listed below:

If the third classification result is a class 4 signature, classification stops and there is a class 4 PD.

If the third classification result is a class 0 or class 1 signature, the devices continues to the fourth cycle classification.

If the third classification result is class 2 or class 3 signature, the type 4 PSE performs a fourth and fifth cycle classification.

The MP8030 PD performs a class signature signal with the CLSA pin in the first and second class cycles. The MP8030 PD performs a class signature signal with the CLSB pin in the remaining class cycles, unless  $V_{\text{DD}}$  drops to its mark event reset threshold.

Both CLSA and CLSB use the same 1.16V output voltage for classification. The maximum output current is limited for protection.

#### **Auto-Class Function**

IEEE802.3bt also supports an auto-class function that allows the PD to communicate its effective maximum power consumption to the PSE. When MP8030 PD auto-class function is enabled (by pulling the AUTOCLS pin low), the PD switches the class current to class 0 within

76ms to 87ms. After the first long time classification function works, this class 0 classification current lasts until the first class is complete.

The auto-class function can indicate to a type 3 or 4 PSE that it supports the auto-class function.

## Under-Voltage Lockout (UVLO) and the Power Supply Voltage

The MP8030 PD integrates one under-voltage lockout (UVLO) circuit with a large hysteresis. The UVLO block ensures that the PD starts up when  $V_{DD}$  exceeds 40V and shuts down when  $V_{DD}$  drops below 30V.

The MP8030 PD also has an inrush current limit during start-up. This current is about 1/7 of the steady state current limit configured by the ILIM pin.

#### **Hot-Swap MOSFET and Current Limit**

The MP8030 PD interface integrates one 100V MOSFET for output disconnect.

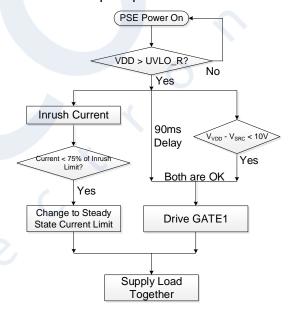

When the PD voltage is powered by the PSE, and  $V_{DD}$  exceeds the rising UVLO threshold, the hot-swap MOSFET starts passing a limited current ( $I_{INRUSH}$ ) to charge the DC/DC converter's input bulk capacitor. The inrush current limit function works until it drops below 75% of the inrush current limit, and then the current limit changes to the normal current limit threshold.

To meet the different power ratings, the MP8030 PD supports a configurable current limit with the ILIM pin. The ILIM pin sources a current after  $V_{\text{DD}}$  rises to the UVLO threshold. This current detects the configured current limit level. Table 2 shows the ILIM configurations.

**Table 2: ILIM Configurations**

| ILIM to G | ND Resist | Current Limit |     |

|-----------|-----------|---------------|-----|

| Min       | Min Typ   |               | (A) |

| 0         | 0         | 1.4           | 0.9 |

| 5.76      | 7.15      | 9.09          | 1.6 |

The GATE1 pin can drive one external N-channel MOSFET, which is connected in parallel with the internal 0.35 $\Omega$  MOSFET. GATE1 turns on the external MOSFET after t<sub>DELAY</sub> (about 90ms) completes. If V<sub>DD</sub> - V<sub>SRC</sub> exceeds 10V after this delay, GATE1 does not turn on because over-current protection (OCP)

is triggered. If  $V_{\text{SRC}}$  is below  $V_{\text{DD}}$  by less than 10V, GATE1 turns on to charge the bulk capacitor. The MP8030 PD turns off the external MOSFET under light-load conditions.

The internal MOSFET and external MOSFET have different current limit control loops. The internal MOSFET current limit is configured by the ILIM pin, while the external MOSFET current limit is configured by a resistor ( $R_{\text{SENSE}}$ ) between the VDD and SENSE pins. To reduce additional power loss and cost, the external MOSFET current limit can be disabled by removing  $R_{\text{SENSE}}$  (connecting the SENSE pin to the VDD pin). It is recommended for  $R_{\text{SENSE}}$  to be  $18\text{m}\Omega$ . When an external  $R_{\text{SENSE}}$  is used, it is recommended to connect the ILIM pin to GND for the lowest total current limit.

Figure 2 shows the internal and external MOSFET start-up sequence.

Figure 2: Internal MOSFET and External MOSFET Start-Up Sequence

The internal and external MOSFETs have fast-off current protection if there is a short-circuit event. After GATE1 turns off, the internal MOSFET recovers if  $V_{\text{IN}}$  -  $V_{\text{SRC}}$  < 10V.

If an overload event occurs when both the internal MOSFET and external MOSFET are connected, the current limit function can work in a few ways, described below:

If the internal MOSFET triggers a current limit first, the internal current is limited, and

additional current goes through the external MOSFET. If the external MOSFET also reaches its current limit, the external MOSFET pulls GATE1 low and V<sub>SRC</sub> drops. If  $V_{DD}$  -  $V_{SRC}$  exceeds 10V for 1ms, the external MOSFET turns off, and the internal MOSFET current limit switches to the inrush limit threshold. At the same time, PG pulls low to disable the DC/DC controller, then works in a new start cycle with the inrush current limit. During this over-current condition, PG recovers without a 90ms delay after the inrush completes.

- If the external MOSFET triggers the current limit first, GATE1 pulls low. Additional current passes through the internal MOSFET and finally triggers the internal current limit. V<sub>SRC</sub> drops after both current limits are triggered and finally runs into current foldback mode (inrush current limit). At the same time, PG is pulled low.

- If the internal MOSFET or external MOSFET triggers the fast-off current limit. the MP8030 PD quickly turns off the related MOSFET then restarts with a delay.

#### Power Good (PG) and Delay

The MP8030 PD has one PG output to enable the DC/DC controller after the inrush period finishes and the PSE is ready to provide high power. PG is an open-drain output with up to a 100V voltage rating.

PG is in high impedance when the device meets the below conditions:

- The device has changed to the steady current limit, which means that the inrush period is complete.

- The 90ms delay (t<sub>DELAY</sub>) from UVLO has completed.

Then a wall power adapter is detected on AUX, and V<sub>ADP</sub> exceeds its UVLO threshold (see Figure 3).

The PG signal resets when VDD UVLO\_F is triggered, if over-temperature protection (OTP) occurs, or if  $V_{DD}$  -  $V_{SRC}$  > 10V for more than 1ms. The 90ms timer only works after  $V_{\text{DD}}$ UVLO is triggered.

Figure 3: PG Logic

#### **PSE and Allocated Power Indicators**

IEEE802.3bt supports 4 different PSE power supplies. The BT, TYP1, and TYP2 pins indicate the PSE-allocated power type. Table 3 on page 28 lists the detailed power level indicators. Note that the indicator only shows high when it is in logic high and pulled up to a high voltage through an external pull-up resistor.

The TYP1, TYP2, and BT signals are active after toelay (about 90ms). The outputs become inactive (high impedance) when the input voltage (V<sub>DD</sub>) falls below its UVLO threshold, or if OTP is triggered. The BT, TYP1, and TYP2 signals are latched in the MP8030 PD after start-up and do not reset until V<sub>DD</sub> drops to its mark event reset threshold.

The TYP1 and TPY2 pins go low if an adapter is detected. BT is high under this condition.

Table 4 on page 28 shows demotion cases.

| Table 3.1 OE and Anocated 1 ower maleator |                                          |                                    |                        |      |      |      |  |  |  |

|-------------------------------------------|------------------------------------------|------------------------------------|------------------------|------|------|------|--|--|--|

| PSE Type                                  | PD Class                                 | PSE Allocated Power                | Number of Class Cycles | ВТ   | TYP1 | TYP2 |  |  |  |

| Type 1<br>Type 2                          | Class 0<br>Class 1<br>Class 2<br>Class 3 | 12.95W<br>3.84W<br>6.49W<br>12.95W | 1                      | High | High | High |  |  |  |

| Type 2                                    | Class 4                                  | 25.5W                              | 2                      | High | High | Low  |  |  |  |

| Type 3                                    | Class 0<br>Class 1<br>Class 2<br>Class 3 | 12.95W<br>3.84W<br>6.49W<br>12.95W | 1                      | Low  | High | High |  |  |  |

| Type 4                                    | Class 4                                  | 25.5W                              | 2, 3                   | Low  | High | Low  |  |  |  |

|                                           | Class 5<br>Class 6                       | 40W<br>51W                         | 4                      | Low  | Low  | High |  |  |  |