# HT32F67595 **Datasheet**

32-Bit Arm® Cortex®-M33/M0+ Dual Core BLE Microcontroller, up to 1024 KB Flash, 256 KB SRAM and 256 KB ROM with BLEC, 2P4GC, DMAC, STIM, GPTM, WDT, RTC, SPI, DSPI, QSPI, UART, I2C, SCI, IrDA, I2S, PCM, AES128, TRNG, QEI, ADC, TSEN

Revision: V1.00 Date: December 09, 2024

www.holtek.com

# **Table of Contents**

| 1 | General Description6                               | 6 |

|---|----------------------------------------------------|---|

| 2 | Features7                                          | 7 |

|   | Main-Processor – MP                                |   |

|   | Co-Processor – CP                                  |   |

|   | On-Chip Memory                                     |   |

|   | Debug Support8                                     |   |

|   | Bluetooth Low Energy Controller – BLEC             |   |

|   | 2.4G RF Private Protocol Controller – 2P4GC        |   |

|   | Reset Control Unit – RSTCU                         |   |

|   | Clock Control Unit – CKCU9                         |   |

|   | Power Management Control Unit – PMU                |   |

|   | DMA Controller – DMAC                              |   |

|   | I/O Ports – GPIO                                   |   |

|   | System Tick Timer – STIM                           |   |

|   | General-Purpose Timer – GPTM                       |   |

|   | Watchdog Timer – WDT12                             |   |

|   | Real Time Clock – RTC                              |   |

|   | Serial Peripheral Interface – SPI                  |   |

|   | Universal Asynchronous Receiver Transmitter – UART |   |

|   | Inter-Integrated Circuit – I <sup>2</sup> C        |   |

|   | Smart Card Interface – SCI                         |   |

|   | Inter-IC Sound – I <sup>2</sup> S                  | 1 |

|   | Cryptography14                                     |   |

|   | Security                                           |   |

|   | Quadrature Encoder Interface – QEI                 | 5 |

|   | Analog to Digital Converter – ADC                  |   |

|   | Temperature Sensor – TSEN                          | 5 |

|   | Package and Operation Temperature                  |   |

| 3 | Overview16                                         | 3 |

|   | Device Information                                 | 3 |

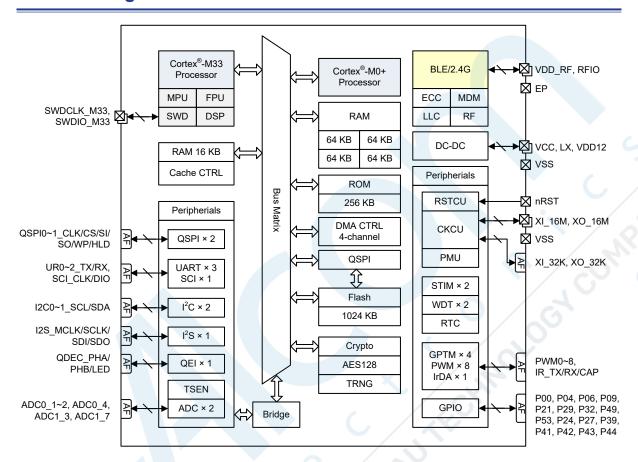

|   | Block Diagram                                      | 7 |

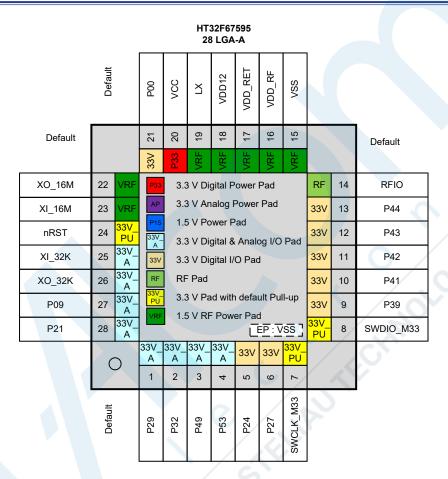

| 4 | Pin Assignment                                     | 3 |

| 5 Electrical Characteristics     | 22                |

|----------------------------------|-------------------|

|                                  | 22                |

|                                  | 22                |

|                                  | 22                |

|                                  | 23                |

| External Clock Characteristics   | 23                |

| Internal Clock Characteristics   | 24                |

| RF Characteristics               | 24                |

|                                  | 25                |

| ADC Characteristics              | 26                |

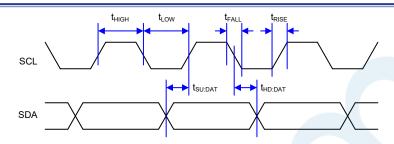

| I <sup>2</sup> C Characteristics | 26                |

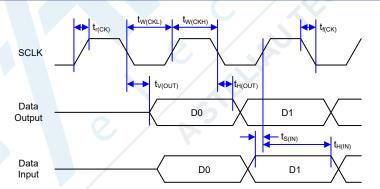

| SPI Characteristics              | 27                |

| TSEN Characteristics             |                   |

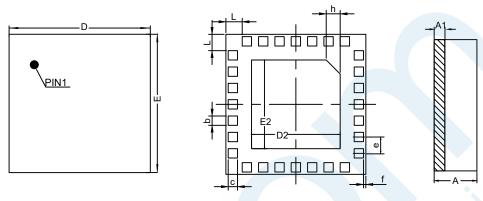

| 6 Package Information            | 29                |

|                                  | utline Dimensions |

# **List of Tables**

| Table 1. Features and Peripheral List                            | 16 |

|------------------------------------------------------------------|----|

| Table 2. Pin Assignment                                          | 19 |

| Table 3. Alternate Function Mapping                              | 20 |

| Table 4. Pin Description                                         | 21 |

| Table 5. Absolute Maximum Ratings                                | 22 |

| Table 6. Recommended Operating Conditions                        | 22 |

| Table 7. Power Consumption Characteristics                       | 22 |

| Table 8. Vcc Power Reset Characteristics                         | 23 |

| Table 9. 16 MHz External Crystal Oscillator Characteristics      | 23 |

| Table 10. 32.768 kHz External Crystal Oscillator Characteristics | 24 |

| Table 11. 32 kHz Internal RC Oscillator Characteristics          | 24 |

| Table 12. 16 MHz Internal RC Oscillator Characteristics          | 24 |

| Table 13. 48 MHz Internal RC Oscillator Characteristics          | 24 |

| Table 14. Radio RX Characteristics                               | 24 |

| Table 15. Radio TX Characteristics                               | 25 |

| Table 16. I/O Port Characteristics                               | 25 |

| Table 17. ADC Characteristics                                    | 26 |

| Table 18. I <sup>2</sup> C Characteristics                       |    |

| Table 19. SPI Characteristics                                    | 27 |

| Table 20. TSEN Characteristics                                   | 28 |

# **List of Figures**

| Figure 1. | Block Diagram                   | <br>17 |

|-----------|---------------------------------|--------|

| Figure 2. | 28-pin LGA Pin Assignment       | <br>18 |

| Figure 3. | nRST Pin Block Diagram          | <br>23 |

|           | I <sup>2</sup> C Timing Diagram |        |

| Figure 5. | SPI Timing Diagram              | <br>27 |

|           | TSEN Operation Diagram          |        |

# **1** General Description

The Holtek HT32F67595 device is a high performance, low power consumption 32-bit microcontroller based around an Arm® Cortex®-M33 processor core and with an Arm® Cortex®-M0+ co-processor core which runs the lower layer of the BLE and 2.4G protocol stack. The Cortex®-M33 is a next-generation processor core which is tightly coupled with Nested Vectored Interrupt Controller (NVIC), SysTick timer, and including advanced debug support.

The device operates at a frequency of up to 64 MHz with a Flash accelerator to obtain maximum efficiency. It provides up to 1024 KB encryptable in-system Flash memory with 16 KB cache controller for code/data storage, up to 256 KB of embedded SRAM memory for system operation and application program usage and up to 256 KB of embedded ROM memory for preprogrammed embedded RTX-RTOS kernel, driver library, and BLE lower layer protocol stack software. A variety of peripherals, such as BLEC, 2P4GC, DMAC, STIM, GPTM, WDT, RTC, SPI, DSPI, QSPI, UART, I<sup>2</sup>C, SCI, IrDA, I<sup>2</sup>S, PCM, AES128, TRNG, QEI, ADC, TSEN and SW-DP (Serial Wire Debug Port), etc., are also implemented in the device. Several power saving modes provide the flexibility for maximum optimization between wake-up latency and power consumption, an especially important consideration in low power applications.

The above features ensure that the device is suitable for use in a wide range of BLE products such as handheld products, health care products, home appliances, smart device information beacons, data loggers, human interface device service, etc.

Rev. 1.00 6 of 31 December 09, 2024

# **2** Features

### Main-Processor - MP

- 32-bit Arm® Cortex®-M33 main processor core

- Up to 64 MHz operating frequency

- 1.5 DMIPS/MHz

- Architecture optimized for small-footprint embedded applications

- Outstanding processing performance combined with fast interrupt handling

- Fast code execution permits slower processor clock or increases sleep mode time

- Efficient processor core, system, and memories

- Low-power consumption with integrated sleep modes

- Serial wire trace reduces the number of pins required for debugging and tracing

The Cortex®-M33 processor provides a high-performance of 1.5 DMIPS/MHz and low-power consumption, while delivering outstanding computational performance and exceptional system response to interrupts.

The CPU executes code from flash using a 16 KB cache controller. Code in flash might be encrypted, so, decryption will happen while in progress without extra wait states.

### Co-Processor - CP

- 32-bit Arm® Cortex®-M0+ processor core

- 16 MHz operating frequency

- 0.93 DMIPS/MHz

The Cortex®-M0+ processor executes code from a dependent 64K Bytes SRAM memory. The code and data can be encrypted and stored in other non-volatile memory such as Flash memory and be dynamically uploaded by software when the device is powered on, which runs the lower layer of the BLE and 2.4G protocol stack.

# **On-Chip Memory**

- Up to 1024 KB in-system Flash memory with 16 KB cache controller for code/data and options storage

- Up to 256 KB of embedded SRAM memory for system operation and application program usage

- Up to 256 KB of embedded ROM memory for preprogrammed embedded RTX-RTOS kernel, driver library, and BLEC lower layer protocol stack software.

The in-system flash memory provides non-volatile storage for code and data.

The ROM provides preprogrammed embedded RTX-RTOS kernel, driver library, and BLEC lower layer protocol stack software. It also contains a boot loader that can be used to reprogram the device using SPI or UART. Since ROM contains BLE host and controller software libraries, leaving more of the flash memory available for the customer applications.

Rev. 1.00 7 of 31 December 09, 2024

Up to 256K Bytes SRAM used for both store the Cortex $^8$ -M33 code & data and Cortex $^8$ -M0+ code. It is split into  $4 \times 64$ K Bytes blocks, each block should be enabled or disabled individually by software to minimize power consumption when system in low power mode. In additional it contains a 16K bytes flash cache. When it is not used, the cache can be used as a general-purpose SRAM.

### **Debug Support**

- 2-Wire SWD debugging

- Supports over-the-air (OTA) upgrade

# **Bluetooth Low Energy Controller – BLEC**

- 2.4 GHz RF transceiver compatible with Bluetooth Low Energy (BLE) 5.3 specification

- Operating clock 16 MHz

- Low power modes supporting 32.768 kHz

- Four operating modes: Active, Sleep, Deep-Sleep and Hibernation

- GFSK modulation, Frequency-Hopping Spread Spectrum (FHSS)

- Support LE 1 Mbps, 2 Mbps and coded 500 Kbps, 125 Kbps for long-range

- Support AoA/AoD for direction finding

- Receiver supports programmable gain control of over 70 dB

- Excellent receiver sensitivity of -96 dBm @ 1 Mbps

- Programmable transmitter output power up to +10 dBm

- All device classes support: Broadcaster, Central, Observer, Peripheral

- Simultaneous Master and Slave operation

- Frequency Hopping

- All packet types: Advertising, Data, Control

- Encryption: AES, CCM

- Bit stream processing: CRC, Whitening

The BLE core is a qualified Bluetooth baseband controller compatible with the Bluetooth Smart specification and it is in charge of packet encoding/decoding and frame scheduling. It performs Link Layer Control management supporting the main BLE states, including advertising and connection.

### 2.4G RF Private Protocol Controller - 2P4GC

- 2.4 GHz RF transceiver

- FSK/GFSK modulation

- Programmable 8/16/80-bit preamble

- Wake-on Radio

- Auto CRC-16

### Reset Control Unit - RSTCU

- System Resets

- Power On Reset POR

- Brown Out Detector BOD

- Low Voltage Detector LVD

- Watchdog Time-out reset

- Software-initiate reset of digital peripherals

There are several sources of reset, some are triggered due to errors or unexpected behavior, while others are user initiated.

### **Clock Control Unit - CKCU**

- External 16 MHz crystal (±20 ppm) oscillator

- External 32.768 kHz crystal (±50 ppm) oscillator

- Internal 16 MHz / 48 MHz RC oscillator

- Internal 32 kHz RC oscillator

- Integrated system clock PLL

- Independent clock divider and gating bits for peripheral clock sources

The CKCU support two external and two internal clock sources. A 16 MHz crystal is required as the frequency for the radio. This signal is doubled internally to create a 64 MHz clock by PLL. Bluetooth low energy requires a slow-speed clock with better than ±50 ppm accuracy if the device is to enter any low power mode while maintaining a connection. The internal 32 kHz RC oscillator can in some use cases be compensated to meet the requirement. The low-speed crystal oscillator is designed for use with a 32.768 kHz crystal. The internal high speed PLL (64 MHz) can be used as a clock source for the main processor, Arm® Cortex®-M33, subsystem. The 32 kHz clock source can be used as external clocking referenced through GPIO.

# Power Management Control Unit – PMU

- Single V<sub>DD</sub> power supply: 1.8 V to 3.6 V

- On-Chip internal SISO DC/DC

- To minimize power consumption, PMU supports a number of software configurable power mode and power management features

| Power Mode Function Block | Active<br>(ACT) | Sleep<br>(SLP) | Deep-Sleep<br>(DSLP) | Hibernation<br>(HIB) |

|---------------------------|-----------------|----------------|----------------------|----------------------|

| CPU                       | Active          | Off            | Off                  | Off                  |

| FLASH                     | On              | Available      | Off                  | Off                  |

| SRAM                      | On              | On             | Off                  | Off                  |

| RADIO                     | On              | Off            | Off                  | Off                  |

| SRAM Retention            | Full            | Partial        | No                   | No                   |

| 16M RC / Crystal          | On              | Off            | Off                  | Off                  |

| 32K RC / Crystal          | On              | On             | On                   | Off                  |

| Power Mode Function Block | Active<br>(ACT) | Sleep<br>(SLP) | Deep-Sleep<br>(DSLP) | Hibernation<br>(HIB) |

|---------------------------|-----------------|----------------|----------------------|----------------------|

| Peripheral                | Available       | Available      | Off                  | Off                  |

| Wake up on RTC            | Available       | Available      | Available            | Off                  |

| Wake up on GPIO           | Available       | Available      | Available            | Available            |

In the Active mode, the application Cortex®-M33 or Cortex®-M0+ CPU is actively executing code. The Active mode provides normal operation of the processor and all of the peripherals that are currently enabled. The system clock can be any available clock source.

In the Sleep mode, all active peripherals can be clocked. But the application CPU core and memory are not clocked, and no code is executed. Any interrupt event will bring the processor back into active mode.

In the Deep-Sleep mode, only the always-on domain is active. An external wake-up event RTC event is required to bring the device back to active mode.

In the Hibernation mode, the device is turned off entirely, including the always-on domain. The I/O are latched with the value they had before entering hibernation mode. A change of state on any I/O pin defined as a wake-up from hibernation pin wakes up the device and functions as a reset trigger.

### **DMA Controller - DMAC**

- Support memory to memory, memory to peripheral, peripheral to memory and peripheral to peripheral transmission

- Support UART, SPI, I<sup>2</sup>C, SCI, I<sup>2</sup>S, ADC interface

- 4 independent DMA channels

- Configurable 2 level priority

- Independent source and destination transfer size (8-bit, 16-bit, 32-bit)

- Support circular mode

- Up to 65535 programmable number of data to be transferred

- Source and destination address increment or no increment

The DMA controller provides a way to offload data transfer tasks from the CPU, allowing for more efficient use of the processor and the available bus bandwidth. The DMA controller can perform transfers between memory and peripherals. The controller has dedicated channels for each supported on-chip module and can be programmed to automatically perform transfers between peripherals and memory as the peripheral is ready to transfer more data.

### I/O Ports - GPIO

- Up to 16 GPIOs

- Programmable driver strength up to 10 mA

- Fully flexible digital pin multiplexing allows use as GPIO or any of several peripherals functions

- Pin state can be retained during all sleep modes

- Pins configured as digital inputs are Schmitt-triggered

- Programmable control for GPIO pad configuration

- Weak pull-up or pull-down resistors

- Digital input enables

- Programmable control for interrupts

- POR Interrupt generation masking per pin

- Edge-triggered on rising or falling

There are up to 16 general purpose I/O pins, GPIO, for the implementation of logic input/output functions. Each of the GPIO ports can be multiplexed to any digital peripheral through the I/O controller which has a series of related control and configuration registers to maximize flexibility and to meet the requirements of a wide range of applications.

# System Tick Timer - STIM

- 32-bit compare match count-up counter no I/O control features

- One shot mode counting stops after a match condition

- Repetitive mode restarts counter after a match condition

There are two dependent system tick timers (STIM), which provide a 48-bit incrementing wrapon-zero counter with a flexible control mechanism. The system tick timer can be used in several different ways.

# **General-Purpose Timer – GPTM**

- 16-bit or 32-bit operating modes

- 16-bit or 32-bit programmable one-shot timer

- 16-bit or 32-bit programmable periodic timer

- 16-bit general-purpose timer with a 4-bit prescaler

- 16-bit input-edge count or time-capture mode with 4-bit prescaler

- 16-bit PWM mode with 4-bit prescaler and software configurable output inversion

- Count Mode

- Power On Reset POR

- Count Up Mode

- Continue Count Up Mode

- Count Up-Down Mode

- Continue Up-Down Mode

- Four 32-bit counter or up to eight 16-bit counters

- Up to eight PWM pins

- Efficient transfers using the DMA controller

- Two 32-bit Timers support IR output to specific pins

- Capture Mode

- IR decode function with capture mode

Rev. 1.00 11 of 31 December 09, 2024

The general-purpose timers can be used to count or time external events that drive the timer-input pins. Each 16 or 32-bit GPTM block provides two 16-bit timers or counters that can be configured to operate independently as timers or event counters or configured to operate as on 32-bit timer.

## Watchdog Timer - WDT

- Two 32-bit counter up with 30.52 µs step for a maximum 36.41 hr time-out

- Non-Maskable Interrupt (NMI) or WDT reset

- NMI interrupt can be selected masked 16 × 30.52 µs ahead before WDT reset

The watchdog timer is used to regain control when system fails because of a software error, or an external device failed to respond properly.

There are two dependent watchdog timers, which can generate a reset when a predefined timer-out value is reached. Two internal 32K RC oscillators provide dependent clock source for two watchdog timers.

### Real Time Clock - RTC

- 48-bit incrementing counter with support for programmable increment to support ppm-adjustment

- Four match registers supporting the generation of events

- Software and hardware reset of events

The Real Time Clock implements a second and sub-second counter with support for soft-compensation for ppm-offsets, with four match registers.

# Serial Peripheral Interface – SPI

- SPI clock frequency up to 16 MHz and programmable output frequencies in master mode

- 8 bytes transmit and receive FIFO

- SPI mode 0, 1, 2, 3 support (clock edge and phase)

- Support both master and slave modes

- Support Multi-master and multi-slave operation

- Support RX timeout interrupt

- Programmable TX only / RX only / TRX mode

- Programmable SPI\_DO idle byte

This interface supports a subset of the Serial Peripheral Interface SPI. The serial interface can transmit and receive 8, 16, 32 bits or as long as data in master/slave mode. Data is written from a master (CPU/DMA) over the APB bus to the SPI.

# **Universal Asynchronous Receiver Transmitter – UART**

- Programmable serial data baud rate

- Hardware flow control support (CTS/RTS)

- Functionality based on the 16550 industry standard

- Programmable character properties, such as number of data bits per character ( $5\sim8$ ), optional

- Parity bit (with odd/even/stick/no select) and number of stop bits (1, 1.5 or 2)

- 8 bytes transmit and receive FIFOs

- Support line break generation and detection

- Support RX timeout interrupt

The UART is compliant to the industry-standard 16550 and is used for serial communication with a peripheral data set. Data is written from a master (CPU/DMA) over the APB bus to the UART and it is converted to serial form and transmitted to the destination device. Serial data is also received by the UART and stored for the master (CPU/DMA) to read back. Both UARTs support hardware flow control signals (RTS, CTS).

### Inter-Integrated Circuit - I<sup>2</sup>C

- Two-wire I<sup>2</sup>C serial interface consists of a serial data line (SDA) and a serial clock (SCL)

- Support three speed modes:

- Standard mode: 0 ~ 100K bit/s

- Fast mode:  $\leq 400$ K bit/s

- High-speed mode:  $\leq$  3M bit/s

- Support 8 bytes transmit/receive FIFOs

- Configurable master or slave, transmit/receive operation

- Support 7-bit or 10-bit addressing mode

- Support configurable slave address and target address

- Interrupt operation

The I<sup>2</sup>C interface is a programmable control bus that provides support for the communications link between Integrated Circuits in a system. It is a simple two-wire bus with a software-defined protocol for system control, which is used in temperature sensors and voltage level translators to EEPROMs, general-purpose I/O, A/D and D/A converters.

### **Smart Card Interface – SCI**

- Support the asynchronous protocols T=0 in accordance with ISO 7816-3

- Flexible output clock 1/2/4 MHz

- Error management at character level for T=0 that parity error counter in reception mode and in transmission mode with auto-repetition

- 32-bit counting by ETU clock for time-out counter

- Power-down mode for reducing current consumption when no activity

The smart card interface is compatible with the ISO 7816-3 and EMV 4.2 related standards. As a master device, it can transmit data controlled by CPU/DMA to destination card, and also it can receive data stored in SRAM.

Rev. 1.00 13 of 31 December 09, 2024

### Inter-IC Sound - I2S

- Master and Slave mode

- I<sup>2</sup>S-justified, Left-justified and DSP (PCM A&B) formats

- 16-bit, 20-bit, 24-bit operation

- Programmable MCLK output: 16/8/4/2 MHz

- Programmable sample rate f<sub>s</sub>: 8/16/32 kHz

The I<sup>2</sup>S is a synchronous communication interface that can be used as a master or slave to exchange data with other audio peripherals, such as ADCs or DACs.

# **Cryptography**

### Advanced Encryption Standard - AES128

- Supports AES Encrypt / Decrypt functions

- Supports AES ECB/CBC/CTR modes

- Supports Key Size of 128 bits

- Supports 4 words Initial Vector for CBC and CTR modes

- $\blacksquare$  4 × 32-bit AES data buffer

- DMA support

- Supports Word Data Swap function

The AES core supports both encryption and decryption functions and supports 128-bit input data. It should be noted that hardware does not pad out any input data bits, therefore users need to do pad action by software at first.

#### **True Random Number Generator – TRNG**

■ TRNG used to provide the seed for encryption processes, its output can be used as entropy input for a Crypto engine

The crypto engine could work in bypass mode and aims to accelerate the algorithm calculations that are needed in order to implement the AES and CBC crypto.

# **Security**

- Supports 32-bit Unique ID for each chip

- Supports automatic hardware decoding

The security module used to protect the code saved in the flash memory, it supports encrypted storage of code for each chip. A 32-bit unique ID is used as the encryption key and each chip can perform the same function but store different code. The user can also use the security module to encrypt the BOOT program.

Rev. 1.00 14 of 31 December 09, 2024

### Quadrature Encoder Interface - QEI

■ Support 2-channel incremental encode

A quadrature encoder, also known as a 2-channel incremental encoder, converts linear displacement into a pulse signal. By monitoring both the number of pulses and the relative phase of the two signals, you can track the position, direction of rotation, and speed. In addition, a third channel, or index signal, can be used to reset the position counter. The quadrature encoder interface (QEI) interprets the code produced by a quadrature encoder wheel to integrate position over time and determine direction of rotation. In addition, it can capture a running estimate of the velocity of the encoder wheel.

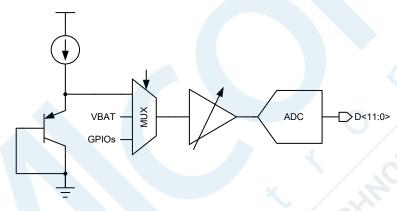

# Analog to Digital Converter - ADC

- Up to 14-bit dynamic SAR ADC engine

- Conversion time and dynamic range can be changed

- 14-bit dynamic with 125 ksps for audio application

- 12-bit dynamic with 500 ksps for general application

- Up to 5 single-ended channels

- One channel for battery monitoring

- DMA support

The low power general purpose 14-bit ADC has up to 5 channels and operates in the single ended mode.

# **Temperature Sensor – TSEN**

■ Detection range:  $-40 \, ^{\circ}\text{C} \sim 125 \, ^{\circ}\text{C}$

■ Accuracy: ±8 °C

■ Resolution: 0.3 °C

A BJT based temperature sensor is integrated, which can be used for performance tuning over temperatures. The sensed voltage is converted to 12-bit digital code by general purpose ADC. Accuracy compensation could be implemented by customer if required.

# **Package and Operation Temperature**

- 28-pin LGA package

- Operation temperature range: -40 °C to 85 °C

Rev. 1.00 15 of 31 December 09, 2024

# **3** Overview

# **Device Information**

**Table 1. Features and Peripheral List**

| Pe                    | ripherals                | HT32F67595     |  |  |  |  |

|-----------------------|--------------------------|----------------|--|--|--|--|

| In-System Flash (KB)  |                          | 1024           |  |  |  |  |

| ROM (KB)              |                          | 256            |  |  |  |  |

| SRAM (KB)             |                          | 256            |  |  |  |  |

|                       | STIM (System Tick Timer) | 2              |  |  |  |  |

| Timers                | GPTM                     | 4              |  |  |  |  |

| Timers                | WDT                      | 2              |  |  |  |  |

|                       | RTC                      | 1              |  |  |  |  |

|                       | QSPI (SPI/DPI/QPI)       | 2              |  |  |  |  |

|                       | UART                     | 3              |  |  |  |  |

| Communication         | I <sup>2</sup> C         | 2              |  |  |  |  |

| Communication         | SCI (ISO7816-3)          | 1              |  |  |  |  |

|                       | IrDA                     | 1              |  |  |  |  |

|                       | I <sup>2</sup> S/LJF/PCM | 1              |  |  |  |  |

| AES-128               |                          | X 1            |  |  |  |  |

| TRNG                  |                          | 1              |  |  |  |  |

| QEI (Quadrature Encod | er I/F)                  | 1              |  |  |  |  |

| 14-bit ADC            | Number of ADCs           | 2              |  |  |  |  |

| 14-bit ADC            | Number of channels       | 5              |  |  |  |  |

| TSEN (Temperature ser | nsor)                    | 1              |  |  |  |  |

| GPIO                  | ( ), ( )                 | Up to 16       |  |  |  |  |

| CPU frequency         |                          | Up to 64 MHz   |  |  |  |  |

| Operating voltage     | 0 /2                     | 1.8 V ~ 3.6 V  |  |  |  |  |

| Operating temperature | V / Y                    | -40 °C ~ 85 °C |  |  |  |  |

| Package               |                          | 28-pin LGA     |  |  |  |  |

| Package               |                          | 28-pin LGA     |  |  |  |  |

## **Block Diagram**

Figure 1. Block Diagram

# 4

# **Pin Assignment**

Figure 2. 28-pin LGA Pin Assignment

Table 2. Pin Assignment

| Package |           |      |        |        |        |                   |                        |        |       |           |                            |

|---------|-----------|------|--------|--------|--------|-------------------|------------------------|--------|-------|-----------|----------------------------|

| 28 LGA  | Default   | GPIO | ADC×2  | IrDA×1 | CLKOUT | SPI/DPI/<br>QPI×2 | I <sup>2</sup> C<br>×3 | UART×3 | PWM×8 | QEI<br>×1 | I <sup>2</sup> S/<br>PCM×1 |

| 28      | P21       |      | ADC0_2 |        |        | V                 | V                      | V      | V     | V         | V                          |

| 1       | P29       |      |        |        | 16MOUT | V                 | V                      | V      | V     | V         | V                          |

| 2       | P32       |      | ADC0_4 |        |        | V                 | V                      | V      | V     | V         | V                          |

| 3       | P49       |      | ADC1_3 |        |        | V                 | V                      | V      | V     | V         | V                          |

| 4       | P53       |      | ADC1_7 |        |        | V                 | V                      | V      | V     | V         | V                          |

| 5       | P24       |      |        |        |        | V                 | V                      | V      | V     | V         | V                          |

| 6       | P27       |      |        |        |        | V                 | V                      | V      | V     | V         | V                          |

| 7       | SWCLK_M33 |      |        |        |        |                   |                        |        |       |           |                            |

| 8       | SWDIO_M33 |      |        |        |        |                   |                        |        |       |           |                            |

| 9       | P39       |      |        |        | 32KOUT | V                 | V                      | V      | V     | V         | V                          |

| 10      | P41       |      |        |        |        | V                 | V                      | V      | V     | V         | V                          |

| 11      | P42       |      |        |        | 32KOUT | V                 | V                      | V      | V     | V         | V                          |

| 12      | P43       |      |        |        |        | V                 | V                      | V      | V     | V         | V                          |

| 13      | P44       |      |        |        |        | V                 | V                      | V      | V     | V         | V                          |

| 14      | RFIO      |      |        |        |        |                   |                        |        |       | Ca        |                            |

| 15      | VSS       |      |        |        |        |                   |                        |        |       |           |                            |

| 16      | VDD_RF    |      |        |        |        |                   | 4                      |        |       |           |                            |

| 17      | VDD_RET   |      |        |        |        |                   |                        |        |       |           |                            |

| 18      | VDD12     |      |        |        |        |                   |                        |        |       |           |                            |

| 19      | LX        |      |        |        |        |                   |                        | .63    |       |           |                            |

| 20      | VCC       |      |        |        |        |                   |                        |        |       |           |                            |

| 22      | XO_16M    |      |        |        |        |                   |                        |        |       |           |                            |

| 23      | XI_16M    |      |        |        |        | / .               | $\bigcirc$             |        |       |           |                            |

| 24      | nRST      |      |        |        |        |                   |                        |        |       |           |                            |

| 21      | P00       |      |        | IR_TX  |        | V                 | V                      | V      | V     | V         | V                          |

| 25      | XI_32K    | P04  |        |        | / _    |                   |                        |        |       |           |                            |

| 26      | XO_32K    | P06  |        |        | / 0    | )                 |                        |        |       |           |                            |

| 27      | P09       |      | ADC0_1 | /      |        | V                 | V                      | V      | V     | V         | V                          |

Note: Alternate Function "V": Programmable

**Table 3. Alternate Function Mapping**

| PID | Function           | PID | Function  | PID | Function           | PID | Function           | PID | Function       |

|-----|--------------------|-----|-----------|-----|--------------------|-----|--------------------|-----|----------------|

| 0   | GPIO               | 16  | SPI1_CLK  | 32  | I2S0_ODATA         | 48  | GPTM1_CAP1         | 64  | GPTM3_B_DECODE |

| 1   | UART0_CTS          | 17  | SPI1_MISO | 33  | I2S0_BCLK          | 49  | GPTM1_A_PWM        | 109 | CLKOUT         |

| 2   | UART0_RXD          | 18  | SPI1_CS   | 34  | I2S0_WCLK          | 50  | GPTM1_B_PWM        | 113 | ADC0_TRIG      |

| 3   | UART0_RTS          | 19  | SPI1_MOSI | 35  | I2S0_SDATA         | 51  | GPTM1_A_<br>DECODE | 117 | ADC1_TRIG      |

| 4   | UART0_TXD          | 20  | SPI0_CLK  | 36  | I2S0_MCLK          | 52  | GPTM1_B_<br>DECODE |     |                |

| 5   | UART1_CTS          | 21  | SPI0_MISO | 37  | QDEC_PHA           | 53  | GPTM2_CAP0         |     |                |

| 6   | UART1_RXD          | 22  | SPI0_CS   | 38  | QDEC_PHB           | 54  | GPTM2_CAP1         |     |                |

| 7   | UART1_RTS          | 23  | SPI0_MOSI | 39  | QDEC_LED           | 55  | GPTM2_A_PWM        |     | Ţ (,           |

| 8   | UART1_TXD          | 24  |           | 40  | GPTM0_<br>CAP0     | 56  | GPTM2_B_PWM        |     | • /            |

| 9   | UART2_CTS          | 25  | _         | 41  | GPTM0_<br>CAP1     | 57  | GPTM2_A_<br>DECODE |     |                |

| 10  | UART2_RXD          | 26  | I2C0_SCL  | 42  | GPTM0_A_<br>PWM    | 58  | GPTM2_B_<br>DECODE |     | 1, (0)         |

| 11  | UART2_RTS          | 27  | I2C0_SDA  | 43  | GPTM0_B_<br>PWM    | 59  | GPTM3_CAP0         |     | 6              |

| 12  | UART2_TXD          | 28  | I2C1_SCL  | 44  | GPTM0_A_<br>DECODE | 60  | GPTM3_CAP1         |     |                |

| 13  | 7816_UAM_<br>CLK   | 29  | I2C1_SDA  | 45  | GPTM0_B_<br>DECODE | 61  | GPTM3_A_PWM        | 1   | 0              |

| 14  | 7816_UAM_<br>DAT   | 30  | I2C2_SCL  | 46  | GPTM_IR_<br>OUT    | 62  | GPTM3_B_PWM        |     |                |

| 15  | 7816_UAM_<br>RST_N | 31  | I2C2_SDA  | 47  | GPTM1_<br>CAP0     | 63  | GPTM3_A_<br>DECODE |     |                |

**Table 4. Pin Description**

| Pin Number |           |                     | I/O                      |                | Description              |                 |

|------------|-----------|---------------------|--------------------------|----------------|--------------------------|-----------------|

| 28 LGA     | Pin Name  | Type <sup>(1)</sup> | Structure <sup>(2)</sup> | Output Driving | Default Function         | Common Function |

| 28         | P21       | AI/O                | 33V                      | 2/4/8/10 mA    | P21                      | ADC0_2          |

| 1          | P29       | AI/O                | 33V                      | 2/4/8/10 mA    | P29                      | _               |

| 2          | P32       | AI/O                | 33V                      | 2/4/8/10 mA    | P32                      | ADC0_4          |

| 3          | P49       | AI/O                | 33V                      | 2/4/8/10 mA    | P49                      | ADC1_3          |

| 4          | P53       | AI/O                | 33V                      | 2/4/8/10 mA    | P53                      | ADC1_7          |

| 5          | P24       | I/O                 | 33V                      | 2/4/8/10 mA    | P24                      | QSPI1_CS        |

| 6          | P27       | I/O                 | 33V                      | 2/4/8/10 mA    | P27                      | QSPI1_HLD       |

| 7          | SWCLK_M33 | I                   | 33V_PU                   | _              | SWCLK_M33                |                 |

| 8          | SWDIO_M33 | I/O                 | 33V_PU                   | _              | SWDIO_M33                | _               |

| 9          | P39       | I/O                 | 33V                      | 2/4/8/10 mA    | P39                      | 32KOUT          |

| 10         | P41       | I/O                 | 33V                      | 2/4/8/10 mA    | P41                      |                 |

| 11         | P42       | I/O                 | 33V                      | 2/4/8/10 mA    | P42                      | 32KOUT          |

| 12         | P43       | I/O                 | 33V                      | 2/4/8/10 mA    | P43                      | / = >           |

| 13         | P44       | I/O                 | 33V                      | 2/4/8/10 mA    | P44                      | 16MOUT          |

| 14         | RFIO      | AI/O                | 12V                      | _              | RF I/O                   | (G) —           |

| 15         | VSS       | Р                   | _                        |                | RF power ground          | <u> </u>        |

| 17         | VDD_RF    | Р                   | _                        | _              | VDD for RF Block         | _               |

| 16         | VDD_RET   | Р                   | _                        | _              | VDD for Retention        | _               |

| 18         | VDD12     | Р                   | _                        | _              | DC-DC Output (1.2 V)     | _               |

| 19         | LX        | AO                  | 12V                      | _              | DC-DC switching output   | _               |

| 20         | VCC       | Р                   | 33V                      | _(_            | Power Supply (1.8~3.6 V) | _               |

| 22         | XO_16M    | AO                  | 12V                      |                | External 16 MHz DCXO XO  | _               |

| 23         | XI_16M    | Al                  | 12V                      | 0 - /          | External 16 MHz DCXO XI  | _               |

| 24         | nRST      | I                   | 33V_PU                   | V_/ .          | External reset pin       | _               |

| 21         | P00       | I/O                 | 33V                      | 2/4/8/10 mA    | P00                      | IR_TX           |

| 25         | XI_32K    | I/O                 | 33V                      | 2/4/8/10 mA    | XI_32K                   | P04             |

| 26         | XO_32K    | I/O                 | 33V                      | 2/4/8/10 mA    | XO_32K                   | P06             |

| 27         | P09       | AI/O                | 33V                      | 2/4/8/10 mA    | P09                      | ADC0_1          |

Note: 1. I = Input, O = Output, A = Analog Port, P = Power Supply

<sup>2. 33</sup>V = 3.3 V tolerant, PU = Pull-up, 12V = 1.2 V, 50V = 5.0V tolerant

<sup>3.</sup> The EP means the exposed pad on the packages. It must be connected to ground.

# **5** Electrical Characteristics

## **Absolute Maximum Ratings**

The following table shows the absolute maximum ratings of the device. These are stress ratings only. Stresses beyond absolute maximum ratings may cause permanent damage to the device. Note that the device is not guaranteed to operate properly at the maximum ratings. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

**Table 5. Absolute Maximum Ratings**

| Symbol           | Parameter                                         | Min.                  | Max.                  | Unit |

|------------------|---------------------------------------------------|-----------------------|-----------------------|------|

| $V_{CC}$         | External Main Supply Voltage                      | V <sub>SS</sub> - 0.3 | V <sub>SS</sub> + 3.6 | V    |

| $V_{IN}$         | Input Voltage on I/O                              | V <sub>SS</sub> - 0.3 | $V_{DD} + 0.3$        | V    |

| T <sub>A</sub>   | Ambient Operating Temperature Range               | -40                   | 85                    | °C   |

| T <sub>STG</sub> | Storage Temperature Range                         | -65                   | 150                   | °C   |

| TJ               | Maximum Junction Temperature                      | _                     | 125                   | °C   |

| V <sub>ESD</sub> | Electrostatic Discharge Voltage – Human Body Mode | -2500                 | 2500                  | V    |

# **Recommended Operating Conditions**

### **Table 6. Recommended Operating Conditions**

T<sub>A</sub> = 25 °C, unless otherwise specified.

| Symbol    | Parameter                        | Conditions                              | Min. | Тур. | Max. | Unit |

|-----------|----------------------------------|-----------------------------------------|------|------|------|------|

| Vcc       | Main Operating Voltage           | , - , , , , , , , , , , , , , , , , , , | 1.8  | 3.3  | 3.6  | V    |

| $V_{ADC}$ | ADC Input Voltage                | <u> </u>                                | 0.0  | _    | 1.1  | V    |

| Vosc      | Crystal Oscillator Input Voltage | _                                       | 0.5  | _    | 1.2  | V    |

# **Power Consumption**

### **Table 7. Power Consumption Characteristics**

$T_A$  = 25 °C,  $V_{CC}$  = 3.0 V and  $V_{DD\_RET}$  = 1.1 V, unless otherwise specified.

| Symbol            | Parameter           | C                  | Conditions                   | Min. | Тур. | Max. | Unit |

|-------------------|---------------------|--------------------|------------------------------|------|------|------|------|

| LDO Mod           | de                  |                    |                              |      |      |      |      |

|                   | Cortox® M33 por MHz |                    | Internal RC                  | 59   | 62   | 65   | μΑ   |

|                   | Cortex®-M33 per MHz |                    | External 16 MHz Crystal      | 70   | 75   | 80   | μΑ   |

|                   | Radio RX            |                    | @ 1 Mbps PHY                 | _    | 10.3 | 11.1 | mA   |

| I <sub>ACT</sub>  |                     |                    | @ 2 Mbps PHY                 | _    | 10.4 | 11.1 | mA   |

|                   | Radio TX            | @ 0 dBm            | _                            | 10.4 | 11.1 | mA   |      |

|                   |                     |                    | @ 10 dBm                     | _    | 32.1 | 35.3 | mA   |

| 1                 | Sloop               |                    | 256K SRAM Retention          | 4.9  | 5.4  | 5.9  | μΑ   |

| I <sub>SLP</sub>  | Sleep               | 64K SRAM Retention | 3.0                          | 3.2  | 3.8  | μΑ   |      |

| I <sub>DSLP</sub> | Deep-Sleep          |                    | RTC On, External 32K Crystal | _    | 2.5  | 2.6  | μA   |

| $I_{HIB}$         | Hibernation         |                    | RTC Off                      | _    | 1.9  | 2.4  | μΑ   |

| Symbol            | Parameter               | Conditions                   | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------|------------------------------|------|------|------|------|

| DC/DC N           | Mode <sup>(Note)</sup>  |                              |      |      |      |      |

|                   | Cortex®-M33 per MHz     | Internal RC                  | _    | 53.5 | _    | μΑ   |

| I <sub>ACT</sub>  | Cortex - Iwos per Iwinz | External 16 MHz Crystal      |      | 55.1 | _    | μΑ   |

|                   | Radio RX                | @ 1 Mbps PHY                 | _    | 4.0  | 4.4  | mA   |

|                   | Tradio Trx              | @ 2 Mbps PHY                 | _    | 3.8  | 4.4  | mA   |

|                   | Radio TX                | @ 0 dBm                      | _    | 3.8  | 4.5  | mA   |

|                   |                         | @ 10 dBm                     | _    | 18   | 24   | mA   |

| 1                 | Sleep                   | 256K SRAM Retention          | 2.6  | 2.9  | 3.1  | μΑ   |

| ISLP              | Sieep                   | 64K SRAM Retention           | 2.3  | 2.5  | 2.75 | μΑ   |

| I <sub>DSLP</sub> | Deep-Sleep              | RTC On, External 32K Crystal | _    | 2.65 | 2.9  | μΑ   |

| $I_{HIB}$         | Hibernation             | RTC Off                      | _    | 1.85 | 2.05 | μΑ   |

Note: Please note that the real current in the DC/DC mode depends on the inductor component selection.

### **Reset Characteristics**

Table 8. Vcc Power Reset Characteristics

$T_A = 25 \, ^{\circ}\text{C} \, \& \, V_{\text{CC}} = 3.0 \, \text{V}$ , unless otherwise specified.

| Symbol           | Parameter         | Conditions                      | Min. | Тур. | Max. | Unit |

|------------------|-------------------|---------------------------------|------|------|------|------|

| R <sub>PU</sub>  | Resistor          | V <sub>CC</sub> = 3.3 V         | 100  | 110  | 120  |      |

|                  |                   | V <sub>CC</sub> = 3.0 V         | 110  | 125  | 140  | kΩ   |

|                  |                   | V <sub>CC</sub> = 2.5 V         | 130  | 160  | 190  |      |

|                  |                   | V <sub>CC</sub> = 1.8 V         | 260  | 290  | 320  |      |

| t <sub>PUS</sub> | Reset Input Pulse | 1.8 V < V <sub>CC</sub> < 3.6 V |      | _    | 100  | ns   |

Figure 3. nRST Pin Block Diagram

## **External Clock Characteristics**

Table 9. 16 MHz External Crystal Oscillator Characteristics

$T_A = 25$  °C &  $V_{CC} = 3.0$  V, unless otherwise specified.

| Symbol             | Parameter                    | Conditions                   | Min. | Тур. | Max. | Unit |

|--------------------|------------------------------|------------------------------|------|------|------|------|

| ESR                | Equivalent Series Resistance | 6 pF < C <sub>L</sub> < 9 pF | _    | 20   | 120  | Ω    |

| CL                 | Crystal Load Capacitance     | _                            | 3    | _    | 27   | pF   |

| f <sub>HSE</sub>   | Crystal Frequency            | _                            | _    | 16   | _    | MHz  |

| FT <sub>HSE</sub>  | Crystal Frequency Tolerance  | _                            | -20  | _    | 20   | ppm  |

| t <sub>HSESU</sub> | Start-up Time                | _                            | 1.3  | 1.5  | 2.3  | ms   |

| TOL <sub>HSE</sub> | Crystal Tolerance            | T <sub>A</sub> = 25 ± 3 °C   | _    | _    | ±10  | ppm  |

|                    |                              | T <sub>A</sub> = -20 ~ 75 °C | _    | _    | ±10  | ppm  |

Table 10. 32.768 kHz External Crystal Oscillator Characteristics

$T_A$  = 25 °C &  $V_{CC}$  = 3.0V, unless otherwise specified.

| Symbol             | Parameter                    | Conditions                   | Min. | Тур.   | Max. | Unit |

|--------------------|------------------------------|------------------------------|------|--------|------|------|

| ESR                | Equivalent Series Resistance | 6 pF < C <sub>L</sub> < 9 pF | _    | 30     | 100  | Ω    |

| CL                 | Crystal Load Capacitance     | _                            | 3    | _      | 27   | pF   |

| f <sub>LSE</sub>   | Crystal Frequency            | _                            | _    | 32.768 | _    | kHz  |

| FT <sub>LSE</sub>  | Crystal Frequency Tolerance  | _                            | -50  | _      | 50   | ppm  |

| t <sub>LSESU</sub> | Start-up Time                | _                            | _    | 3      | _    | ms   |

### **Internal Clock Characteristics**

### Table 11. 32 kHz Internal RC Oscillator Characteristics

T<sub>A</sub> = 25 °C & V<sub>CC</sub> = 3.0V, unless otherwise specified.

| Symbol               | Parameter                                |    |        | Conditions    | Min.  | Тур.  | Max.  | Unit   |

|----------------------|------------------------------------------|----|--------|---------------|-------|-------|-------|--------|

| f <sub>IRC32K</sub>  | Internal 32 kHz RC Oscillation Frequency | Ca | alibra | ate Frequency | 32.62 | 32.81 | 32.90 | kHz    |

| TC <sub>IRC32K</sub> | Temperature Coefficient                  |    |        | _             | _     | 80    |       | ppm/°C |

### Table 12. 16 MHz Internal RC Oscillator Characteristics

$T_A = 25$  °C &  $V_{CC} = 3.0V$ , unless otherwise specified.

| Symbol               |                | Parar    | neter       |     |        |          | Co    | nditions | Min.  | Тур. | Max.  | Unit   |

|----------------------|----------------|----------|-------------|-----|--------|----------|-------|----------|-------|------|-------|--------|

| f <sub>IRC16M</sub>  | Internal 16 MH | z RC C   | Oscillation | Fre | quency | Calibrat | te Fı | requency | 15.68 | 16.0 | 16.32 | MHz    |

| TC <sub>IRC16M</sub> | Temperature C  | oefficie | ent         |     |        |          |       | _        | 70    | 80   | 90    | ppm/°C |

#### Table 13. 48 MHz Internal RC Oscillator Characteristics

$T_A$  = 25 °C &  $V_{CC}$  = 3.0V, unless otherwise specified.

| Symbol                | Parameter                                | Conditions          | Min.  | Тур. | Max.  | Unit   |

|-----------------------|------------------------------------------|---------------------|-------|------|-------|--------|

| $f_{IRC48M}$          | Internal 48 MHz RC Oscillation Frequency | Calibrate Frequency | 45.68 | 48.0 | 48.30 | MHz    |

| TC <sub>IRC48M</sub>  | Temperature Coefficient                  | 0. /- 2             | 70    | 80   | 90    | ppm/°C |

| t <sub>IRC48MSU</sub> | Start-up Time                            |                     | _     | 8    | 10    | μs     |

### **RF Characteristics**

#### **Table 14. Radio RX Characteristics**

$T_A = 25$  °C,  $V_{CC} = 3.0V$  & LDO Mode, unless otherwise specified.

| Symbol           | Parameter                                                  | Min.  | Тур.  | Max. | Unit |

|------------------|------------------------------------------------------------|-------|-------|------|------|

| P <sub>MIN</sub> | Sensitivity                                                | -94.5 | -96   | -97  | dBm  |

| In-Band          | Blocking                                                   |       |       |      |      |

| C <sub>I0</sub>  | Co-channel Interference                                    | _     | -3    | _    | dB   |

| C <sub>I1</sub>  | Interferer at f <sub>OFFS</sub> = +1/-1 MHz                | _     | 9/5   | _    | dB   |

| C <sub>I2</sub>  | Interferer at f <sub>OFFS</sub> = +2/-2 MHz                | _     | 43/42 | _    | dB   |

| C <sub>I3</sub>  | Interferer at f <sub>OFFS</sub> = +3/-3 MHz                | _     | 47/42 | _    | dB   |

| C <sub>14</sub>  | Interferer at Image Channel (f <sub>IMAGE</sub> )          | _     | 32    | _    | dB   |

| C <sub>15</sub>  | Interferer at Image Channel (f <sub>IMAGE</sub> +1/-1 MHz) | _     | 5/12  | _    | dB   |

| Out-of-B         | and Blocking                                               |       |       |      |      |

|                  | f = 30 ~ 2,000 MHz                                         | _     | -40   | _    | dBm  |

|                  | f = 2,000 ~ 2,399 MHz                                      | _     | -19   | _    | dBm  |

|                  | f = 2,484 ~ 3,000 MHz                                      | _     | -22   | _    | dBm  |

|                  | f = 3,000 ~ 12,750 MHz                                     | _     | -42   | _    | dBm  |

| Symbol            | Parameter                                                                                       | Min. | Тур. | Max. | Unit |  |

|-------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|--|

| Intermo           | Intermodulation Performance for Wanted Signal                                                   |      |      |      |      |  |

|                   | at -64 dBm and 1 Mbps BLE, 3 <sup>rd</sup> , 4 <sup>th</sup> and 5 <sup>th</sup> Offset Channel | _    | -37  | _    | dBm  |  |

| P <sub>ISSI</sub> | Upper Limit of Monotonous Range                                                                 | _    | -94  | _    | dBm  |  |

#### **Table 15. Radio TX Characteristics**

$T_A$  = 25 °C,  $V_{CC}$  = 3.0V & LDO Mode, unless otherwise specified.

| Symbol               | Parameter                                        | Min.         | Тур. | Max.    | Unit |

|----------------------|--------------------------------------------------|--------------|------|---------|------|

| P <sub>TX</sub>      | Output Power                                     | -45          | 0    | 10      | dBm  |

|                      | Output Power Step                                | _            | 3    | _       | dBm  |

| $\Delta$ F2AVG       | Average Frequency Deviation for 10101010 Pattern | 185          | 249  | _       | kHz  |

| $\Delta_{\sf F1AVG}$ | Average Frequency Deviation for 11110000 Pattern | 225          | 247  | 275     | kHz  |

|                      | $\Delta_{\sf F2AVG}$ / $\Delta_{\sf F1AVG}$      | 8.0          | 1    | _       | _/   |

| Carrier              | Frequency Accuracy                               | -150         | 0    | 150     | kHz  |

|                      | Maximum Frequency Drift                          | -20          | 0    | 20      | kHz  |

|                      | Initial Frequency Drift                          | -23          | 0    | 23      | kHz  |

|                      | Maximum Drift Rate (per 50 µs)                   | -20          | 0    | 20      | kHz  |

| Spurious             | s Emissions                                      |              |      | H       |      |

|                      | f < 1 GHz                                        | J_/          | -21  | <u></u> | dBm  |

|                      | f > 1 GHz including harmonics                    | <del>/</del> | -43  | _       | dBm  |

| In-Band              | Emissions (at 0 dBm, f = 2400 ~ 2483.5 MHz)      |              |      |         |      |

|                      | < f ± 2 MHz                                      | -48          | -44  | -40     | dBm  |

## **I/O Port Characteristics**

### Table 16. I/O Port Characteristics

$T_A = 25 \, ^{\circ}\text{C} \, \& \, V_{\text{CC}} = 3.0 \, \text{V}$ , unless otherwise specified.

| Symbol            | Parameter                     | Conditions              | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------------|-------------------------|------|------|------|------|

|                   |                               | V <sub>CC</sub> = 3.3 V | 105  | 115  | 125  | kΩ   |

| R <sub>PU</sub>   | Bull up Equivalent Posistor   | V <sub>CC</sub> = 3.0 V | 110  | 125  | 135  | kΩ   |

|                   | Pull-up Equivalent Resistor   | V <sub>CC</sub> = 2.5 V | 150  | 160  | 170  | kΩ   |

|                   |                               | V <sub>CC</sub> = 1.8 V | 270  | 290  | 310  | kΩ   |

| R <sub>PD</sub>   |                               | V <sub>CC</sub> = 3.3 V | 65   | 85   | 95   | kΩ   |

|                   | Dull down Equivalent Desigtor | V <sub>CC</sub> = 3.0 V | 80   | 90   | 100  | kΩ   |

|                   | Pull-down Equivalent Resistor | V <sub>CC</sub> = 2.5 V | 105  | 115  | 125  | kΩ   |

|                   |                               | V <sub>CC</sub> = 1.8 V | 185  | 205  | 220  | kΩ   |

|                   | Level-0                       | V <sub>CC</sub> = 3.3 V | 4.8  | 5.0  | 5.2  | mA   |

|                   |                               | V <sub>CC</sub> = 3.0 V | 3.8  | 4.0  | 4.2  | mA   |

| I <sub>DRV0</sub> |                               | V <sub>CC</sub> = 2.5 V | 3.0  | 3.2  | 3.4  | mA   |

|                   |                               | V <sub>CC</sub> = 1.8 V | 1.8  | 2.0  | 2.2  | mA   |

|                   | /                             | V <sub>CC</sub> = 3.3 V | 7.3  | 7.5  | 7.7  | mA   |

| I <sub>DRV1</sub> | Level-1                       | V <sub>CC</sub> = 3.0 V | 6.6  | 6.8  | 7.0  | mA   |

|                   |                               | V <sub>CC</sub> = 2.5 V | 4.8  | 5.0  | 5.2  | mA   |

|                   |                               | V <sub>CC</sub> = 1.8 V | 3.1  | 3.3  | 3.5  | mA   |

| Symbol            | Parameter | Conditions              | Min. | Тур. | Max. | Unit |

|-------------------|-----------|-------------------------|------|------|------|------|

| I <sub>DRV2</sub> | Level-2   | V <sub>CC</sub> = 3.3 V | 9.6  | 9.8  | 10   | mA   |

|                   |           | V <sub>CC</sub> = 3.0 V | 8.8  | 9.0  | 9.2  | mA   |

|                   |           | V <sub>CC</sub> = 2.5 V | 6.6  | 6.8  | 7.0  | mA   |

|                   |           | V <sub>CC</sub> = 1.8 V | 4.0  | 4.2  | 4.4  | mA   |

|                   | Level-3   | V <sub>CC</sub> = 3.3 V | 10.8 | 11.0 | 11.2 | mA   |

| I                 |           | V <sub>CC</sub> = 3.0 V | 9.6  | 9.8  | 10.0 | mA   |

| IDRV3             |           | V <sub>CC</sub> = 2.5 V | 7.5  | 7.7  | 7.9  | mA   |

|                   |           | V <sub>CC</sub> = 1.8 V | 5.2  | 5.4  | 5.6  | mA   |

### **ADC Characteristics**

### **Table 17. ADC Characteristics**

$T_A = 25 \, ^{\circ}\text{C} \, \& \, V_{\text{CC}} = 3.0 \, \text{V}$ , unless otherwise specified.

| Symbol            | Parameter                                   | Conditions                       | Min.       | Тур.                                         | Max.        | Unit               |

|-------------------|---------------------------------------------|----------------------------------|------------|----------------------------------------------|-------------|--------------------|

| V <sub>REF</sub>  | Reference Voltage <sup>(1)</sup>            | _                                | _          | 1.1                                          | _/          | V                  |

| f <sub>ADC</sub>  | Clock Frequency                             | _                                | _          | 4                                            | 8           | MHz                |

| £                 | Compling Data                               | 14-bit                           | _          | 125                                          | -           | ksps               |

| fs                | Sampling Rate                               | 12-bit                           |            | 500                                          |             | ksps               |

| t <sub>TRIG</sub> | External Trigger Period                     | _                                |            |                                              | 10          | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>  | Conversion Voltage Range                    | //- {                            | 0          |                                              | $V_{REFT+}$ | V                  |

| R <sub>AIN</sub>  | External Input Impedance                    | _                                | / /        | <u>)                                    </u> | 10          | ΜΩ                 |

| C <sub>ADC</sub>  | Internal S/H Capacitor Impedance            | -x                               | / -/6      | 5                                            | _           | pF                 |

| t <sub>PU</sub>   | Power-up Time                               | /                                | -          | 1                                            | _           | CC <sup>(2)</sup>  |

| ts                | Sampling Time                               | ( <del>-</del> / ,               | 1.5        | _                                            | 1000        | 1/f <sub>ADC</sub> |

| t <sub>CONV</sub> | Total Conversion Time (Resolution = N bits) | <u> </u>                         | ts+0.5+N/2 | _                                            | _           | 1/f <sub>ADC</sub> |

| ACC               | Acquirequ                                   | V <sub>AIN</sub> < 50 mV         | _          | ±10                                          | _           | LSB                |

|                   | Accuracy                                    | 50 mV < V <sub>AIN</sub> < 50 mV | _          | ±2                                           | ±3          | LSB                |

| ENOB              | Effective Number of Dite                    | Single Ended                     | _          | 11.8                                         | _           | Bits               |

|                   | Effective Number of Bits                    | Differential                     | _          | 13.2                                         | _           | Bits               |

Note: 1. When V<sub>AIN</sub> > V<sub>REFT+</sub>, the ADC convert result is 0xFFF.

2. CC: Conversion Cycle.

### **I**<sup>2</sup>C Characteristics

### Table 18. I<sup>2</sup>C Characteristics

$T_A$  = 25 °C,  $V_{CC}$  = 3.0 V & SCL = 1 MHz, unless otherwise specified.

| Symbol              | Parameter               | Conditions | Min. | Тур. | Max. | Unit |

|---------------------|-------------------------|------------|------|------|------|------|

| fscL                | SCL Clock Frequency     | _          | _    | _    | 1    | MHz  |

| $t_{LOW}$           | SCL Low Level Duration  | _          | 0.6  | _    | _    | μs   |

| t <sub>HIGH</sub>   | SCL High Level Duration | _          | 0.3  | _    | _    | μs   |

| t <sub>RISE</sub>   | SCL, SDA Rise Time      | _          | _    | _    | 0.2  | μs   |

| t <sub>FALL</sub>   | SCL, SDA Fall Time      | _          | _    | _    | 0.2  | μs   |

| t <sub>SU:DAT</sub> | SDA Setup Time          | _          | 0.1  | _    | _    | μs   |

| t <sub>HD:DAT</sub> | SDA Hold Time           | _          | 10   | _    | _    | μs   |

Figure 4. I<sup>2</sup>C Timing Diagram

# **SPI Characteristics**

**Table 19. SPI Characteristics**

T<sub>A</sub> = 25 °C & V<sub>CC</sub> = 3.0 V, unless otherwise specified.

| Symbol              | Parameter              | Conditions                      | Min.      | Тур. | Max.                   | Unit |

|---------------------|------------------------|---------------------------------|-----------|------|------------------------|------|

| 1/tcĸ               | Clock Fraguency        | 2.5 V < V <sub>CC</sub> < 3.6 V | _         | 4    | 32                     | MHz  |

| I/ICK               | Clock Frequency        | 1.8 V < V <sub>CC</sub> < 2.5 V | _         | _    | 20                     | MHz  |

| tw(CKH)             | Clock High Time        | _                               | tck/2-0.5 | _/   | t <sub>ck</sub> /2     | ns   |

| tw(CKL)             | Clock Low Time         | _                               | tck/2     | /    | t <sub>CK</sub> /2+0.5 | ns   |

| t <sub>S(IN)</sub>  | Data Input Setup Time  | - 3                             | 1 /       |      | <b>9</b> _             | ns   |

| t <sub>H(IN)</sub>  | Data Input Hold Time   | _                               | 3.5       |      | _                      | ns   |

| $t_{\text{V(OUT)}}$ | Data Output Valid Time | — ×                             | /- 3      | 1    | 2                      | ns   |

| $t_{\text{H(OUT)}}$ | Data Output Hold Time  |                                 | 0         | _    | _                      | ns   |

Figure 5. SPI Timing Diagram

## **TSEN Characteristics**

### **Table 20. TSEN Characteristics**

$T_A$  = 25 °C &  $V_{CC}$  = 3.0V, unless otherwise specified.

| Symbol              | Parameter                      | Conditions | Min. | Тур. | Max.       | Unit  |

|---------------------|--------------------------------|------------|------|------|------------|-------|

| TC                  | Sensor Temperature Coefficient | _          |      | 2    | _          | mV/°C |

| T <sub>RNG</sub>    | Temperature Sensor Range       | _          |      | _    | 125        | °C    |

| T <sub>ACC</sub>    | Temperature Sensor Accuracy    | _          | -8   | _    | 8          | °C    |

| T <sub>RES</sub>    | Temperature Sensor Resolution  | _          | _    | 0.3  | _          | °C    |

| t <sub>V(OUT)</sub> | Data Output Valid Time         | _          | _    | 0.3  | _          | ns    |

| I <sub>TSEN</sub>   | Temperature Sensor Current     | _          | _    | 20   | <b>)</b> — | μA    |

Figure 6. TSEN Operation Diagram

Rev. 1.00 28 of 31 December 09, 2024

# 6 Package Information

Note that the package information provided here is for consultation purposes only. As this information may be updated at regular intervals users are reminded to consult the <u>Holtek website</u> for the latest version of the <u>Package/Carton Information</u>.

Additional supplementary information with regard to packaging is listed below. Click on the relevant section to be transferred to the relevant website page.

- Package Information (include Outline Dimensions, Product Tape and Reel Specifications)

- The Operation Instruction of Packing Materials

- Carton information

Rev. 1.00 29 of 31 December 09, 2024

# 28-pin LGA (3mm × 3mm × 0.75mm) Outline Dimensions

| Symbol   | Dimensions in inch |       |       |  |  |

|----------|--------------------|-------|-------|--|--|

| Syllibol | Min.               | Nom.  | Max.  |  |  |

| А        | 0.024              | 0.026 | 0.028 |  |  |

| A1       | 0.006              | 0.007 | 0.008 |  |  |

| b        | 0.007              | 0.008 | 0.009 |  |  |

| С        | 0.007              | 0.008 | 0.009 |  |  |

| D        | 0.114              | 0.118 | 0.122 |  |  |

| D2       | 0.071              | 0.075 | 0.079 |  |  |

| е        | 0.013              | 0.014 | 0.015 |  |  |

| E        | 0.114              | 0.118 | 0.122 |  |  |

| E2       | 0.071              | 0.075 | 0.079 |  |  |

| L        | 0.013              | 0.014 | 0.015 |  |  |

| f        | 0.002              | 0.002 | 0.002 |  |  |

| h        | 0.011              | 0.012 | 0.013 |  |  |

| Cumbal | Dimensions in mm |      |       |  |  |  |

|--------|------------------|------|-------|--|--|--|

| Symbol | Min.             | Nom. | Max.  |  |  |  |

| Α      | 0.62             | 0.67 | 0.72  |  |  |  |

| A1     | 0.14             | 0.17 | 0.20  |  |  |  |

| b      | 0.17             | 0.20 | 0.23  |  |  |  |

| С      | 0.17             | 0.20 | 0.23  |  |  |  |

| D      | 2.90             | 3.00 | 3.10  |  |  |  |

| D2     | 1.80             | 1.90 | 2.00  |  |  |  |

| е      | 0.33             | 0.35 | 0.37  |  |  |  |

| E      | 2.90             | 3.00 | 3.10  |  |  |  |

| E2     | 1.80             | 1.90 | 2.00  |  |  |  |

| L /    | 0.33             | 0.35 | 0.37  |  |  |  |

| f      | 0.045            | 0.05 | 0.055 |  |  |  |

| h      | 0.28             | 0.30 | 0.32  |  |  |  |

The information provided in this document has been produced with reasonable care and attention before publication, however, HOLTEK does not guarantee that the information is completely accurate. The information contained in this publication is provided for reference only and may be superseded by updates. HOLTEK disclaims any expressed, implied or statutory warranties, including but not limited to suitability for commercialization, satisfactory quality, specifications, characteristics, functions, fitness for a particular purpose, and non-infringement of any thirdparty's rights. HOLTEK disclaims all liability arising from the information and its application. In addition, HOLTEK does not recommend the use of HOLTEK's products where there is a risk of personal hazard due to malfunction or other reasons. HOLTEK hereby declares that it does not authorise the use of these products in life-saving, life-sustaining or safety critical components. Any use of HOLTEK's products in life-saving/sustaining or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold HOLTEK harmless from any damages, claims, suits, or expenses resulting from such use. The information provided in this document, including but not limited to the content, data, examples, materials, graphs, and trademarks, is the intellectual property of HOLTEK (and its licensors, where applicable) and is protected by copyright law and other intellectual property laws. No license, express or implied, to any intellectual property right, is granted by HOLTEK herein. HOLTEK reserves the right to revise the information described in the document at any time without prior notice. For the latest information, please contact us.