# Arora V series of FPGA Products **Data Sheet**

DS981-1.0E, 09/26/2022

Singel 3 | B-2550 Kontich | Belgium | Tel. +32 (0)3 458 30 33 info@alcom.be | www.alcom.be Rivium 1e straat 52 | 2909 LE Capelle aan den IJssel | The Netherlands Tel. +31 (0)10 288 25 00 | info@alcom.nl | www.alcom.nl

# Copyright © 2022 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

**GOWIN** and GOWIN are trademarks of Guangdong Gowin Semiconductor Corporation and are registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders. No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. All information in this document should be treated as preliminary. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

# Preliminary

# **Revision History**

| Date       | Version | Description                |

|------------|---------|----------------------------|

| 09/26/2022 | 1.0E    | Initial version published. |

#### Contents

# Contents

| Contents                           | i  |

|------------------------------------|----|

| List of Figures                    | iv |

| List of Tables                     | v  |

| 1 About This Guide                 | 1  |

| 1.1 Purpose                        | 1  |

| 1.2 Related Documents              | 1  |

| 1.3 Terminology and Abbreviations  | 1  |

| 1.4 Support and Feedback           | 3  |

| 2 General Description              | 4  |

| 2.1 Features                       | 4  |

| 2.2 Product Resources              | 6  |

| 3 Architecture                     | 7  |

| 3.1 Architecture                   |    |

| 3.2 Configurable Function Unit     | 9  |

| 3.3 Input/Output Block             |    |

| 3.3.1 I/O Buffer                   |    |

| 3.3.2 I/O Logic                    |    |

| 3.3.3 I/O Logic Modes              |    |

| 3.4 Block SRAM (BSRAM)             |    |

| 3.4.1 Introduction                 |    |

| 3.4.2 Configuration Mode           |    |

| 3.4.3 Data Bus Width Configuration |    |

| 3.4.4 ECC (GW5A(T)-138)            |    |

| 3.4.5 Byte-enable                  |    |

| 3.4.6 Synchronous Operation        |    |

| 3.4.7 Power up Conditions          |    |

| 3.4.8 BSRAM Operation Modes        |    |

| 3.4.9 Clock Operations             |    |

| 3.5 DSP                            |    |

| 3.5.1 PADD                         |    |

| 3.5.2 MULT                         |    |

|     | 3.5.3 ALU                                                                 | 27 |

|-----|---------------------------------------------------------------------------|----|

|     | 3.5.4 Operating Mode                                                      | 27 |

|     | 3.6 Gigabit Transceivers (GW5AT-138)                                      | 28 |

|     | 3.7 PCIe 2.0 (GW5AT-138)                                                  | 29 |

|     | 3.8 MIPI D-PHY                                                            | 30 |

|     | 3.8.1 MIPI D-PHY RX (GW5A(T)-138)                                         | 30 |

|     | 3.8.2 MIPI D-PHY RX/TX(GW5A-25)                                           | 30 |

|     | 3.9 Analog to Digital Converter (ADC)                                     | 31 |

|     | 3.10 Clock                                                                | 32 |

|     | 3.10.1 Global Clock                                                       | 32 |

|     | 3.10.2 HCLK                                                               | 32 |

|     | 3.10.3 PLL                                                                | 33 |

|     | 3.10.4 DDR Memory Interface Clock Management DQS                          | 34 |

|     | 3.11 Long Wire (LW)                                                       | 34 |

|     | 3.12 Global Set/Reset (GSR)                                               | 34 |

|     | 3.13 Programming Configuration                                            | 34 |

|     | 3.14 On Chip Oscillator                                                   | 36 |

| 4 / | AC/DC Characteristic                                                      | 37 |

|     | 4.1 Operating Conditions                                                  | 37 |

|     | 4.1.1 Absolute Max. Ratings                                               | 37 |

|     | 4.1.2 Recommended Operating Conditions                                    | 38 |

|     | 4.1.3 Power Rising Slope                                                  | 38 |

|     | 4.1.4 Hot Socket Specifications                                           | 38 |

|     | 4.1.5 POR Specifications                                                  | 39 |

|     | 4.2 Electro-Static Discharge (ESD)                                        | 39 |

|     | 4.3 DC Characteristic                                                     | 39 |

|     | 4.3.1 DC Electrical Characteristics over Recommended Operating Conditions | 39 |

|     | 4.3.2 Static Current                                                      | 40 |

|     | 4.3.3 Recommended I/O Operating Conditions                                | 40 |

|     | 4.3.4 Single ended I/O DC Characteristic                                  | 41 |

|     | 4.3.5 Differential I/O DC Characteristic                                  | 42 |

|     | 4.4 AC Switching Characteristic                                           | 43 |

|     | 4.4.1 CFU Switching Characteristic                                        | 43 |

|     | 4.4.2 BSRAM Switching Characteristic                                      | 43 |

|     | 4.4.3 DSP Switching Characteristic                                        | 43 |

|     | 4.4.4 Clock and I/O Switching Characteristic                              | 44 |

|     | 4.4.5 On chip Oscillator Switching Characteristic                         | 44 |

|     | 4.4.6 PLL Switching Characteristic                                        | 44 |

|     | 4.5 Configuration Interface Timing Specification                          |    |

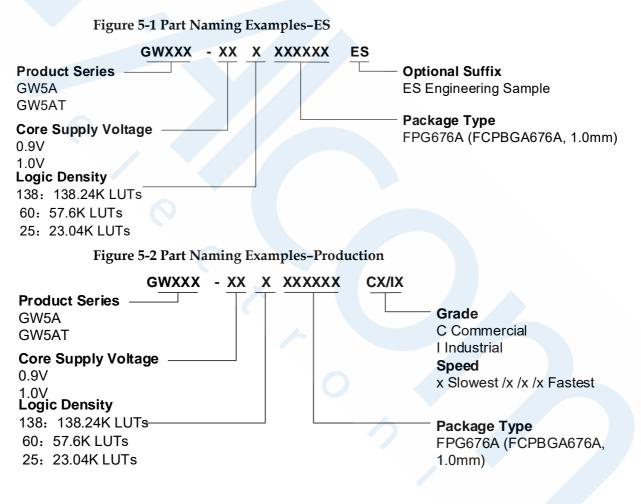

| 5 Or | rdering Information | 45 |

|------|---------------------|----|

| ξ    | 5.1 Part Name       | 45 |

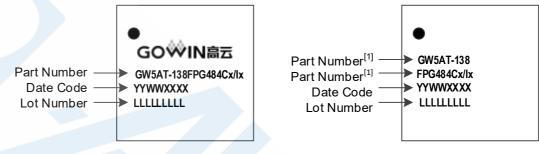

| Ę    | 5.2 Package Mark    | 46 |

# **List of Figures**

| Figure 3-1 Architecture Diagram(GW5AT-138)7                            |   |

|------------------------------------------------------------------------|---|

| Figure 3-2 CFU View                                                    |   |

| Figure 3-3 IOB Structure View                                          | 0 |

| Figure 3-4 Bank Distribution View of Arora V (GW5AT-138) 11            | 1 |

| Figure 3-5 Bank Distribution View of Arora V (GW5A-138) 11             | 1 |

| Figure 3-6 Bank Distribution View of Arora V (GW5A-25) 12              | 2 |

| Figure 3-7 I/O Logic Output                                            | 6 |

| Figure 3-8 I/O Logic Input                                             | 6 |

| Figure 3-9 IODELAY                                                     | 7 |

| Figure 3-10 Register Structure in I/O Logic 17                         | 7 |

| Figure 3-11 Pipeline Mode in Single Port, Dual Port and Semi-Dual Port | 3 |

| Figure 3-12 Independent Clock Mode                                     |   |

| Figure 3-13 Read/Write Clock Mode                                      | 5 |

| Figure 3-14 Single Port Clock Mode                                     | 5 |

| Figure 3-15 Gigabit Transceiver Architecture View                      | 8 |

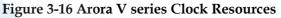

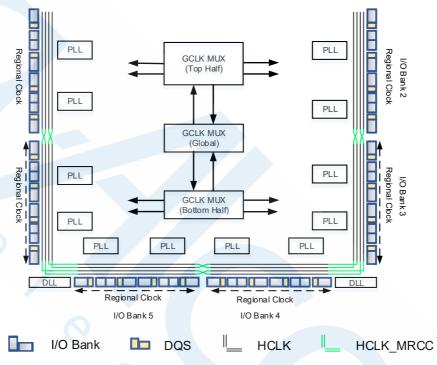

| Figure 3-16 Arora V series Clock Resources                             | 2 |

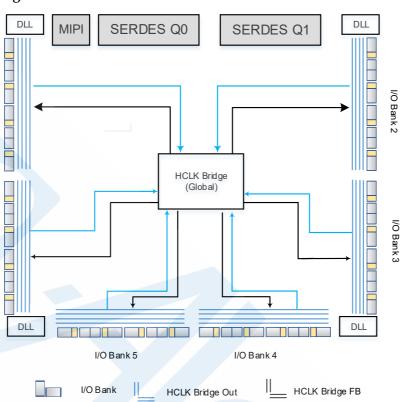

| Figure 3-17 GW5AT HCLK Distribution                                    |   |

| Figure 5-1 Part Naming Examples-ES                                     |   |

| Figure 5-2 Part Naming Examples–Production                             | 5 |

| Figure 5-3 Package Mark Examples                                       | 6 |

# **List of Tables**

| Table 1-1 Terminology and Abbreviations                                                                  | 1  |

|----------------------------------------------------------------------------------------------------------|----|

| Table 2-1 Product Resources                                                                              | 6  |

| Table 2-2 Package Information and Max. User I/O                                                          | 6  |

| Table 3-1 Output I/O Standards and Configuration Options                                                 | 12 |

| Table 3-2 Input I/O Standards and Configuration Options                                                  | 14 |

| Table 3-3 Port Description                                                                               | 16 |

| Table 3-4 Serialization and deserialization ratio modes supported by The Arora V series of FPGA Products |    |

| Table 3-5 Memory Size Configuration                                                                      | 19 |

| Table 3-6 Read/Write Data Width Configuration in Dual Port Mode                                          | 21 |

| Table 3-7 Read/Write Data Width Configuration in Semi Dual Port Mode                                     | 21 |

| Table 3-8 Read/Write Data Width Configuration in Semi Dual Port with ECC Function Mode                   | 22 |

| Table 3-9 Clock Operations in Different BSRAM Modes                                                      | 24 |

| Table 3-10 Oscillator Output Frequency Options                                                           | 36 |

| Table 4-1 Absolute Max. Ratings                                                                          | 37 |

| Table 4-2 Recommended Range                                                                              | 38 |

| Table 4-3 Power Supply Ramp Rate                                                                         | 38 |

| Table 4-4 Hot Socket Specifications                                                                      | 38 |

| Table 4-5 POR Paramrters                                                                                 | 39 |

| Table 4-6 Arora V ESD - HBM                                                                              | 39 |

| Table 4-7 Arora V ESD - CDM                                                                              | 39 |

| Table 4-8 DC Electrical Characteristics over Recommended Operating Conditions                            | 39 |

| Table 4-9 Static Current                                                                                 | 40 |

| Table 4-10 I/O Operating Conditions Recommended                                                          | 40 |

| Table 4-11 Single-ended DC Characteristic                                                                |    |

| Table 4-12 Differential I/O DC Characteristic                                                            | 42 |

| Table 4-13 CFU Timing Parameters                                                                         | 43 |

| Table 4-14 BSRAM Timing Parameters                                                                       | 43 |

| Table 4-15 DSP Timing Parameters                                                                         | 43 |

| Table 4-16 External Switching Characteristics                                                            | 44 |

| Table 4-17 On chip Oscillator Switching Characteristic                                                   | 44 |

| Table 4-18 PLL Switching Characteristic                                                                  | 44 |

# **1** About This Guide

# 1.1 Purpose

This data sheet describes the features, product resources and structure, AC/DC characteristics, timing specifications of the configuration interface, and the ordering information of the Arora V series of FPGA Products, which helps you to understand the Arora V series of FPGA Products quickly and select and use devices appropriately.

# **1.2 Related Documents**

The latest user guides are available on the GOWINSEMI Website. You can find the related documents at <u>www.gowinsemi.com</u>:

- UG983, Arora V series of FPGA Products Package and Pinout Manual

- <u>UG982, GW5AT-138 Pinout</u>

# **1.3 Terminology and Abbreviations**

The terminology and abbreviations used in this manual are as shown in Table 1-1.

## **Table 1-1 Terminology and Abbreviations**

| Terminology and Abbreviations | Full Name                         |

|-------------------------------|-----------------------------------|

| ADC                           | Analog to Digital Converter       |

| AER                           | Advanced Error Reporting          |

| ALU                           | Arithmetic Logic Unit             |

| BSRAM                         | Block Static Random Access Memory |

| CFU                           | Configurable Function Unit        |

| CLS                           | Configurable Logic Section        |

| CRU                           | Configurable Routing Unit         |

| CSI                           | Camera Serial Interface           |

| СТС                           | Clock Tolerance Compensation      |

| Terminology and Abbreviations | Full Name                              |

|-------------------------------|----------------------------------------|

| DCS                           | Dynamic Clock Selector                 |

| DFF                           | D Flip-flop                            |

| DNA                           | Device Identifier                      |

| DP                            | True Dual Port 16K BSRAM               |

| DSI                           | Display Serial Interface               |

| DSP                           | Digital Signal Processing              |

| ECC                           | Error Correcting Code                  |

| ECRC                          | End-to-End Cyclic Redundancy Check     |

| ESD                           | Electro-Static Discharge               |

| FIFO                          | First In First Out                     |

| FPG                           | FCPBGA                                 |

| FPGA                          | Field Programmable Gate Array          |

| GCLK                          | Global Clock                           |

| GPIO                          | Gowin Programmable IO                  |

| GSR                           | Global Set/Reset                       |

| HCLK                          | High Speed Clock                       |

| IOB                           | Input/Output Block                     |

| LUT                           | Look-up Table                          |

| LW                            | Long Wire                              |

| MIPI                          | Mobile Industry Processor Interface    |

| OTP                           | One Time Programmable                  |

| PCle                          | Peripheral Component Interface Express |

| PCS                           | Physical Coding Sublayer               |

| PLL C                         | Phase-locked Loop                      |

| РМА                           | Physical Medium Attachment             |

| REG                           | Register                               |

| SDP                           | Semi Dual Port 16K BSRAM               |

| SP                            | Single Port 16K BSRAM                  |

| SSRAM                         | Shadow Static Random Access Memory     |

| TDM                           | Time Division Multiplexing             |

|                               |                                        |

# **1.4 Support and Feedback**

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly by the following ways.

Website: www.gowinsemi.com

E-mail: <a href="mailto:support@gowinsemi.com">support@gowinsemi.com</a>

# **2** General Description

# 2.1 Features

## **FPGA Fabric Architecture**

- Up to 138K LUTs(GW5A(T)-138)

- Up to 23K LUTs(GW5A-25)

- Block SRAM with multiple modes

- Single Port, Semi-Dual Port, True Dual Port, and Semi Dual Port with ECC function

- Byte write enable

- ECC error detection and correction

- High performance DSP

- Multipliers support 12x12, 27x36, 27x18bit modes

- Includes 48-bit accumulator

- Supports DSP cascading

- Embedded pipeline and bypass registers

- Pre-addtion operation for filter function

- Internal feedback loop and barrel shifter

- Advanced Clocking

- Up to 32 global clocks

- Up to 6/12 high-performance PLLs

- Up to 16/24 high speed edge clocks

#### Flexible GPIO

- Adjustable drive strength

- 4mA, 8mA, 12mA, 16mA, 24mA drive

- Bus keeper, pull up/down and open drain

- Hot Socket and input hysteresis

- Slew Rate option for output signal

#### ADC

- 60dB SNR and 1kHz Signal Bandwidth

- Flexible X-channel oversampling ADC

- No external voltage source required

#### **Configuration & Programming**

- JTAG, SSPI, MSPI, CPU, and SERIAL

- Background programming

- SPI Flash Programming and Boot

Multi-boot

- Bitstream encryption and Security

- SEU error detection and correction

#### **High Speed Interfaces**

- SERDES(GW5AT-138)

- 270Mbps-12.5Gbps operation

- CDR (Clock Data Recovery)

- Dedicated RX and TX Channels

- Integrated 8b/10b encoder/decoder

- PCIe2.0 hardcore

- x1, x2, x4, x8 lanes

- Supports root complex and end point

- MIPI D-PHY RX hardcore(GW5A(T)-138)

- 20Gbps D-PHY RX Hard PHY

- 8 data lanes + 2 clock lanes

- 2.5Gbps/lane

- Built-in SoT HS-Sync, word and lane alignment

- MIPI DSI and MIPI CSI-2 RX link layer IPs

- MIPI D-PHY RX/TX hardcore(GW5A-25)

- 4 data lanes + 1 clock lane

- 2.5Gbps/lane(RX/TX)

- Built-in SoT HS-Sync, word and lane alignment

- MIPI DSI and MIPI CSI-2 RX link layer IPs

- GPIOs support MIPI C-PHY RX/TX and D-PHY RX/TX(GW5A-25)

- 1.2Gbps/lane

- GPIOs can be configured as MIPI DSI and MIPI CSI-2 RX/TX device interface

- GPIOs support MIPI D-PHY RX(GW5AT-138)

- 1.5Gbps/lane

- GPIOs can be configured as MIPI DSI and MIPI CSI-2 RX device interface

- External DRAM Interfaces

- Supports various memory types

- DDR2, DDR3, PSRAM, HyperRAM, RPC

- Up to 1333 Mbps (GW5A(T)-138) or 1066 Mbps (GW5A-25)

• Supports OTP, each device has a unique 64-bit DNA identifer

GOWINSEMI's Arora V FPGA series provides SRAM based FPGA devices with increased logic resources, interfaces and performance. Arora V FPGAs include DDR3 memory interfacing, 12.5Gbps CDR based SERDES supporting multiple protocols and flexible packaging options making it the ideal choice for communications, server, imaging and automotive applications requiring high interface and computing throughput by providing best performance/watt.

Arora V is supported by GOWIN EDA providing an efficient and easy to use FPGA hardware development environment support multiple RTL based programming languages, synthesis, placement & routing, bitstream generation and download, power analysis and in-device logic analyzer.

# **2.2 Product Resources**

| Device                                                  | GW5A-25                                       | GW5AT-60                                      | GW5A-138                                   | GW5AT-138                                  |

|---------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------------------------|--------------------------------------------|

| LUT4                                                    | 23040                                         | 57600                                         | 138240                                     | 138240                                     |

| REG                                                     | 23040                                         | 57600                                         | 138240                                     | 138240                                     |

| Distributed Static Random<br>Access Memory<br>SSRAM(Kb) | 180                                           | 450                                           | 1080                                       | 1080                                       |

| Block Static Random Access<br>Memory<br>BSRAM(Kb)       | 1008                                          | 2322                                          | 6120                                       | 6120                                       |

| Number of BSRAM                                         | 56                                            | 129                                           | 340                                        | 340                                        |

| DSP                                                     | 28                                            | 120                                           | 298                                        | 298                                        |

| Phase Locked Loop (PLLs) <sup>[1]</sup>                 | 6                                             | 10                                            | 12                                         | 12                                         |

| Global Clock                                            | 32                                            | 32                                            | 32                                         | 32                                         |

| HCLK                                                    | 16                                            | 20                                            | 24                                         | 24                                         |

| Transceivers                                            | 0                                             | 4                                             | 0                                          | 8                                          |

| Transceivers Rate                                       | N/A                                           | 270Mbps-<br>12.5Gbps                          | N/A                                        | 270Mbps-<br>12.5Gbps                       |

| PCle 2.0 Hardcore                                       | 0                                             | 1, x1, x2, x4<br>PCle 2.0                     | 0                                          | 1, x1, x2, x4, x8<br>PCle2.0               |

| LVDS Gbps                                               | 1.25                                          | 1.25                                          | 1.25                                       | 1.25                                       |

| DDR3 Mbps                                               | 1066                                          | 1333                                          | 1333                                       | 1333                                       |

| MIPI DPHY Hardcore                                      | 2.5G(RX/TX),<br>4 data lanes,<br>1 clock lane | 2.5G(Rx/Tx),<br>8 data lanes,<br>2 clock lane | 2.5G(RX)<br>8 data lanes,<br>2 clock lanes | 2.5G(RX)<br>8 data lanes,<br>2 clock lanes |

| ADC                                                     | 1                                             | 1                                             | 2                                          | 2                                          |

| Number of GPIO Banks                                    | 9 <sup>[2]</sup>                              | 5                                             | 6                                          | 6                                          |

| Max. I/O                                                | 236                                           | 250                                           | 376                                        | 376                                        |

| Core Voltage                                            | 0.9V/1.0V                                     | 0.9V/1.0V                                     | 0.9V/1.0V                                  | 0.9V/1.0V                                  |

# **Table 2-1 Product Resources**

#### Note!

- [1] Different packages support different numbers of PLLs; up to 12 PLLs can be supported.

- [2] One of the Banks is a JTAG Bank with 4 IOs.

#### Table 2-2 Package Information and Max. User I/O

| Package | Pitch (mm) | Size (mm) | E-pad Size<br>(mm) | GW5AT-138 | GW5A-138 | GW5AT-60 | GW5A-25 |

|---------|------------|-----------|--------------------|-----------|----------|----------|---------|

| FPG676A | 1.0        | 27 x 27   | -                  | 312(150)  | -        | -        | -       |

Note!

The package types in this Arora V sheet are written with abbreviations. See  $\underline{5.1 \text{ Part}}$  Name for further information.

# **3** Architecture

# **3.1 Architecture**

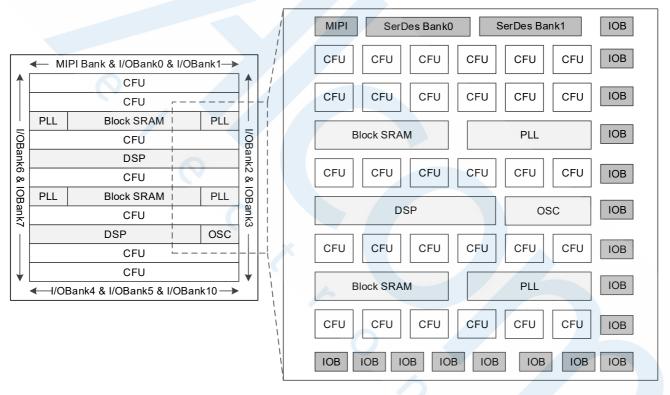

Figure 3-1 Architecture Diagram(GW5AT-138)

See Figure 3-1 for an overview of the architecture of the Arora V series of FPGA Products (GW5AT-138). Please refer to Table 2-1 for GW5AT-138 devices internal resources. The core of device is an array of Configurable Function Unit (CFU) surrounded by IO blocks. Besides, Arora V provides BSRAM, DSP Gigabit Transceiver, MIPI D-PHY, ADC, PLL, and on chip oscillator.

Configurable Function Unit (CFU) is the base cell for the array of the Arora V series of FPGA Products. Devices with different capacities have different numbers of rows and columns. CFU can be configured as LUT4 mode, ALU mode, and memory mode. For more detailed information, see

## 3.2 Configurable Function Unit.

The I/O resources in the Arora V series of FPGA Products are arranged around the periphery of the devices in groups referred to as banks. I/O resources support multiple I/O standards, and support regular mode, SDR mode, generic DDR mode, and DDR\_MEM mode. For more detailed information, see <u>3.3 Input/Output Block</u>.

The BSRAM is embedded as a row in Arora V series of FPGA Products. Each BSRAM has 18,432 Kbits and supports multiple configuration modes and operation modes. For more detailed information, see <u>3.4 Block SRAM (BSRAM)</u>.

Arora V series of FPGA Products are embedded with a brand-new DSP, which can meet your high-performance digital signal processing requirements. For details, refer to <u>3.5 DSP</u>.

Arora V series of FPGA Products(GW5AT-138) include two Gigabit Transceiver Quads, each of which supports up to 4 transceivers. For details, refer to <u>3.6 Gigabit Transceiver</u>.

Arora V series of FPGA Products provide a MIPI D-PHY hardcore supporting MIPI Alliance Standard for D-PHY Specification V1.2. For details, refer to <u>3.8 MIPI D-PHY</u>.

Arora V series of FPGA Products integrate a new and flexible oversampling ADC. For details, refer to <u>3.9</u> Analog to Digital Converter

Arora V series of FPGA Products have embedded PLL resources. PLL blocks provide the ability to synthesize clock frequencies. Frequency adjustment (multiply and division), phase adjustment, and duty cycle can be adjusted using the configuration of parameters. There is an internal programmable on-chip oscillator in each of the Arora V series of the FPGA product. The on-chip oscillator supports the clock frequencies ranging from 2.5 MHz to 105MHz, providing the clock resource for the MSPI mode. It also provides programmable user clocks. For more detailed information, please refer to <u>3.14 On Chip Oscillator.</u>

FPGA provides abundant CRUs, connecting all the resources in FPGA. For example, routing resources distributed in CFU and IOB connect resources in CFU and IOB. Routing resources can automatically be generated by Gowin software. In addition, the Arora V series of FPGA Products also provide abundant GCLKs, long wires (LW), global set/reset (GSR), and programming options, etc. For more details, see <u>3.11 Long</u> <u>Wire (LW), 3.12 Global Set/Reset (GSR), 3.13 Programming</u> <u>Configuration</u>.

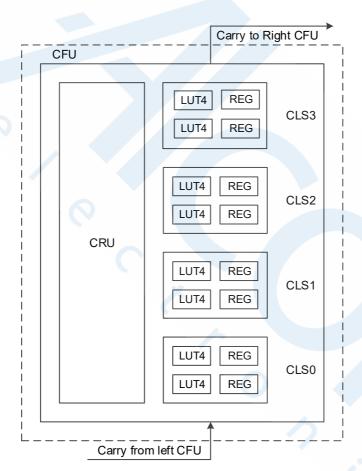

# 3.2 Configurable Function Unit

Configurable Function Units (CFUs) are the basic cells for the array of GOWINSEMI FPGA Products. Each basic cell consists of four Configurable Logic Sections (CLS) and their routing resource Configurable Routing Unit (CRU). Each CLS includes two 4 input look-up-tables (LUT) and two registers (REG), as shown in Figure 3-2.

CLS in the CFU can be configured as basic look-up table, arithmetic logic unit, static random access memory, and read only memory according to application scenarios.

For more details on the CFU, please see UG303, Arora V series Configurable Function Unit (CFU) User Guide.

Figure 3-2 CFU View

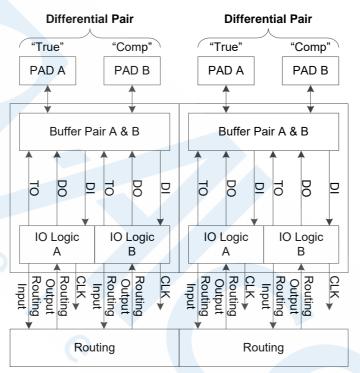

# 3.3 Input/Output Block

The IOB in the Arora V series of FPGA Products includes IO buffer, IO logic, and its routing unit. As shown in Figure 3-3, each IOB connects to two Pins (Marked as A and B). They can be used as a differential pair or as a single end input/output.

Figure 3-3 IOB Structure View

IOB Features:

- Vcco supplied with each bank

- All banks support True differential input

- Supports multiple levels: LVCMOS, PCI, LVTTL, SSTL, HSTL, LVDS, Mini\_LVDS, RSDS, PPDS, BLVDS

- Input hysteresis option

- Output drive strength option

- Slew rate option

- Individual bus keeper, weak pull-up, weak pull-down, and open drain option

- Hot socket

- IO logic supports basic mode, SDR mode, and generic DDR mode

# 3.3.1 I/O Buffer

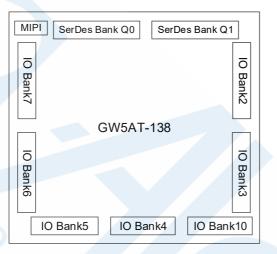

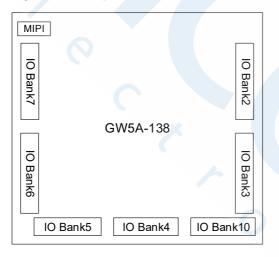

GW5AT-138 includes six GPIO Banks (Bank2~7), two SERDES Banks and a Bank for configuration (Bank 10), as shown in Figure 3-4. Bank 10 can also be used as I/O Bank.

GW5A-138 includes six GPIO Banks (Bank2~7) and a Bank for configuration (Bank 10), as shown in Figure 3-5. Bank 10 can also be used as I/O Bank.

Figure 3-4 Bank Distribution View of Arora V (GW5AT-138)

Figure 3-5 Bank Distribution View of Arora V (GW5A-138)

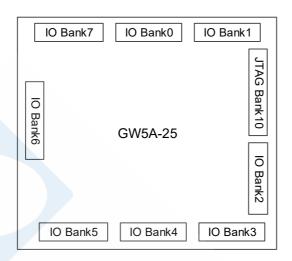

GW5A-25 includes nine GPIO Banks, as shown in Figure 3-6. One of the GPIO Banks is JTAG Bank, including four IOs.

Figure 3-6 Bank Distribution View of Arora V (GW5A-25)

Each Bank has independent I/O power supply V\_{CCO}. V\_{CCO} can be set as 3.3V, 2.5V, 1.8V, 1.5V, 1.35V, 1.2V, or 1V.

To support SSTL, HSTL, etc., each bank also provides one independent voltage source (VREF) as reference voltage. You can choose from the internal reference voltage of the bank (0.6V, 0.675V, 0.75V, 0.9V, and (33%,42%,50%,58%)Vcco) or the external reference voltage using any IO from the bank.

Auxiliary voltage V<sub>CCX</sub> is 1.8V only.

Different banks in the Arora V series of FPGA Products support different on-chip resistor settings, including single-ended resistor and differential resistor. Single-ended resistor is set for SSTL/HSTL I/O. Differential resistor is set for LVDS/PPDS/ RSDS input. For more details,

refer to UG304, Arora V series Programmable IO (GPIO) User Guide.

Note!

GPIO is tri-stated weak pull-up by default.

For the V<sub>CCO</sub> requirements of different I/O standards, see Table 3-1.

| I/O output standard | Single/Differ                | Bank<br>Vcco (V) | Output Driver<br>Strength (mA) | Typical Applications                               |

|---------------------|------------------------------|------------------|--------------------------------|----------------------------------------------------|

| LVDS25              | Differential Pair<br>(TLVDS) | 2.5/3.3          | 3.5/2.5/4.5/6                  | High-speed point-to-<br>point data<br>transmission |

| BLVDS25             | Differential Pair<br>(TLVDS) | 2.5/3.3          | 3.5/2.5/4.5/6                  | Multi-point high-<br>speed data<br>transmission    |

| RSDS                | Differential Pair<br>(TLVDS) | 2.5/3.3          | 3.5/2.5/4.5/6                  | High-speed point-to-<br>point data<br>transmission |

| MINILVDS            | Differential Pair<br>(TLVDS) | 2.5/3.3          | 3.5/2.5/4.5/6                  | LCD timing driver interface and                    |

Table 3-1 Output I/O Standards and Configuration Options

| I/O output standard | Single/Differ                | Bank<br>Vcco (V) | Output Driver<br>Strength (mA) | Typical Applications                                             |

|---------------------|------------------------------|------------------|--------------------------------|------------------------------------------------------------------|

|                     |                              |                  |                                | column driver<br>interface                                       |

| PPLVDS              | Differential Pair<br>(TLVDS) | 2.5/3.3          | 3.5/2.5/4.5/6                  | LCD row/column<br>driver                                         |

| LVDS25E             | Differential                 | 2.5              | 8/4/12/16/24                   | High-speed point-to-<br>point data<br>transmission               |

| BLVDS25E            | Differential                 | 2.5              | 8/4/12/16/24                   | Multi-point high-<br>speed data<br>transmission                  |

| MLVDS25E            | Differential                 | 2.5              | 8/4/12/16/24                   | LCD timing driver<br>interface and<br>column driver<br>interface |

| RSDS25E             | Differential                 | 2.5              | 8/4/12/16/24                   | High-speed point-to-<br>point data<br>transmission               |

| LVPECL33E           | Differential                 | 3.3              | 8/4/12/16/24                   | Universal interface                                              |

| HSUL12D             | Differential                 | 1.2              | 8/4/12                         | LPDDR2                                                           |

| HSUL12D_I           | Differential                 | 1.2              | 8/4/12                         | LPDDR2                                                           |

| HSTL15D_I           | Differential                 | 1.5              | 8/4/12/16                      | Memory interface                                                 |

| HSTL15D_II          | Differential                 | 1.5              | 8/4/12/16                      | Memory interface                                                 |

| HSTL18D_I           | Differential                 | 1.8              | 8/4/12/16                      | Memory interface                                                 |

| HSTL18D_II          | Differential                 | 1.8              | 8/4/12/16                      | Memory interface                                                 |

| SSTL135D            | Differential                 | 1.35             | 8/4/12                         | Memory interface                                                 |

| SSTL15D             | Differential                 | 1.5              | 8/4/12/16                      | Memory interface                                                 |

| SSTL18D_I           | Differential                 | 1.8              | 8/4/12/16/24                   | Memory interface                                                 |

| SSTL18D_II          | Differential                 | 1.8              | 8/4/12/16/24                   | Memory interface                                                 |

| LVCMOS10D           | Differential                 | 1.0              | 4                              | Universal interface                                              |

| LVCMOS12D           | Differential                 | 1.2              | 8/4/12                         | Universal interface                                              |

| LVCMOS15D           | Differential                 | 1.5              | 8/4/12/16                      | Universal interface                                              |

| LVCMOS18D           | Differential                 | 1.8              | 8/4/12/24 <sup>[1]</sup>       | Universal interface                                              |

| LVCMOS25D           | Differential                 | 2.5              | 8/4/12/24 <sup>[1]</sup>       | Universal interface                                              |

| LVCMOS33D           | Differential                 | 3.3              | 8/4/12/24 <sup>[1]</sup>       | Universal interface                                              |

| HSUL12              | Single end                   | 1.2              | 8/4/12                         | Memory interface                                                 |

| HSTL12_I            | Single end                   | 1.2              | 8/4/12                         | Memory interface                                                 |

| HSTL15_I            | Single end                   | 1.5              | 8/4/12/16                      | Memory interface                                                 |

| HSTL15_II           | Single end                   | 1.5              | 8/4/12/16                      | Memory interface                                                 |

| HSTL18_I            | Single end                   | 1.8              | 8/4/12/16/24                   | Memory interface                                                 |

| HSTL18_II           | Single end                   | 1.8              | 8/4/12/16/24                   | Memory interface                                                 |

| SSTL135             | Single end                   | 1.35             | 8/4/12                         | Memory interface                                                 |

| SSTL15              | Single end                   | 1.5              | 8/4/12/16                      | Memory interface                                                 |

| L                   | 1                            | 1                | 1                              | l                                                                |

| I/O output standard  | Single/Differ | Bank<br>Vcco (V) | Output Driver<br>Strength (mA) | Typical Applications    |

|----------------------|---------------|------------------|--------------------------------|-------------------------|

| SSTL18_I             | Single end    | 1.8              | 8/4/12/16/24                   | Memory interface        |

| SSTL18_II            | Single end    | 1.8              | 8/4/12/16/24                   | Memory interface        |

| LVCMOS10             | Single end    | 1.0              | 4                              | Universal interface     |

| LVCMOS12             | Single end    | 1.2              | 8/4/12                         | Universal interface     |

| LVCMOS15             | Single end    | 1.5              | 8/4/12/16                      | Universal interface     |

| LVCMOS18             | Single end    | 1.8              | 8/4/12/16/24 <sup>[1]</sup>    | Universal interface     |

| LVCMOS25             | Single end    | 2.5              | 8/4/12/16/24 <sup>[1]</sup>    | Universal interface     |

| LVCMOS33/LVTTL3<br>3 | Single end    | 3.3              | 8/4/12/16/24 <sup>[1]</sup>    | Universal interface     |

| LPDDR                | Single end    | 1.8              | 8/4/12/16/24 <sup>[1]</sup>    | LPDDR and Mobile<br>DDR |

| PCI33                | Single end    | 3.3              | 8/4/12/16/24 <sup>[1]</sup>    | PC and embedded system  |

#### Note!

GW5A-25 does not support 24mA LVCMOS.

# Table 3-2 Input I/O Standards and Configuration Options

| I/O Input Standard | Single/Differ | Bank Vcco (V)                          | Hysteresis | Need VREF |

|--------------------|---------------|----------------------------------------|------------|-----------|

| MIPI               | Differential  | 1.2                                    | No         | No        |

| LVDS25             | Differential  | 2.5/1.0/1.2/1.5/1.8/3.3                | No         | No        |

| RSDS               | Differential  | 2.5/1.0/1.2/1.5/1.8/3.3                | No         | No        |

| MINILVDS           | Differential  | 2.5/1.0/1.2/1.5/1.8/3.3                | No         | No        |

| PPLVDS             | Differential  | 2.5/1.0/1.2/1.5/1.8/3.3                | No         | No        |

| HSUL12D            | Differential  | 1.2/1.0/1.5/1.8/2.5/3.3                | No         | No        |

| HSTL12D_I          | Differential  | 1.2/1.0/1. <mark>5/1</mark> .8/2.5/3.3 | No         | No        |

| HSTL15D_I          | Differential  | 1.5/1.0/1. <mark>2/1.</mark> 8/2.5/3.3 | No         | No        |

| HSTL15D_II         | Differential  | 1.5/1.0/1.2/1.8/2.5/3.3                | No         | No        |

| HSTL18D_I          | Differential  | 1.8/1.0/1.2/1.5/2.5/3.3                | No         | No        |

| HSTL18D_II         | Differential  | 1.8/1.0/1.2/1.5/2.5/3.3                | No         | No        |

| SSTL135D           | Differential  | 1.35/1.0/1.2/1.5/1.8/2.5<br>/3.3       | No         | No        |

| SSTL15D            | Differential  | 1.5/1.0/1.2/1.8/2.5/3.3                | No         | No        |

| SSTL18D_I          | Differential  | 1.8/1.0/1.2/1.5/2.5/3.3                | No         | No        |

| SSTL18D_II         | Differential  | 1.8/1.0/1.2/1.5/2.5/3.3                | No         | No        |

| LPDDRD             | Differential  | 1.8/1.0/1.2/1.5/2.5/3.3                | No         | No        |

| LVCMOS10D          | Differential  | 1.0/1.2/1.5/1.8/2.5/3.3                | No         | No        |

| LVCMOS12D          | Differential  | 1.2/1.0/1.5/1.8/2.5/3.3                | No         | No        |

| LVCMOS15D          | Differential  | 1.5/1.0/1.2/1.8/2.5/3.3                | No         | No        |

| LVCMOS18D          | Differential  | 1.8/1.0/1.2/1.5/2.5/3.3                | No         | No        |

| HSUL12             | Single end    | 1.2                                    | Yes        | No        |

| I/O Input Standard   | Single/Differ | Bank Vcco (V)    | Hysteresis | Need VREF |

|----------------------|---------------|------------------|------------|-----------|

| HSTL12_I             | Single end    | 1.2              | Yes        | No        |

| HSTL15_I             | Single end    | 1.5              | Yes        | No        |

| HSTL15_II            | Single end    | 1.5              | Yes        | No        |

| HSTL18_I             | Single end    | 1.8              | Yes        | No        |

| HSTL18_II            | Single end    | 1.8              | Yes        | No        |

| SSTL135              | Single end    | 1.35             | Yes        | No        |

| SSTL15               | Single end    | 1.5              | Yes        | No        |

| SSTL18_I             | Single end    | 1.8              | Yes        | No        |

| SSTL18_II            | Single end    | 1.8              | Yes        | No        |

| LVCMOS10             | Single end    | 1.0              | Yes        | No        |

| LVCMOS10UD12         | Single end    | 1.2              | Yes        | No        |

| LVCMOS10UD15         | Single end    | 1.5              | Yes        | No        |

| LVCMOS10UD18         | Single end    | 1.8              | Yes        | No        |

| LVCMOS10UD25         | Single end    | 2.5              | Yes        | No        |

| LVCMOS10UD33         | Single end    | 3.3              | Yes        | No        |

| LVCMOS12             | Single end    | 1.2              | Yes        | No        |

| LVCMOS15             | Single end    | 1.5              | Yes        | No        |

| LVCMOS150D10         | Single end    | 1.0              | Yes        | No        |

| LVCMOS150D12         | Single end    | 1.2              | Yes        | No        |

| LVCMOS15UD18         | Single end    | 1.8              | Yes        | No        |

| LVCMOS15UD25         | Single end    | 2.5              | Yes        | No        |

| LVCMOS15UD33         | Single end    | 3.3              | Yes        | No        |

| LVCMOS18             | Single end    | 1.8              | Yes        | No        |

| LVCMOS180D10         | Single end    | 1.0              | Yes        | No        |

| LVCMOS180D12         | Single end    | 1.2              | Yes        | No        |

| LVCMOS180D15         | Single end    | 1.5              | Yes        | No        |

| LVCMOS18UD25         | Single end    | 2.5              | Yes        | No        |

| LVCMOS18UD33         | Single end    | 3.3              | Yes        | No        |

| LVCMOS25             | Single end    | 2.5              | Yes        | No        |

| LVCMOS25UD33         | Single end    | 3.3              | No         | No        |

| LVCMOS33/<br>LVTTL33 | Single end    | 3.3              | Yes        | No        |

| LVCMOS330D25         | Single end    | 2.5              | Yes        | No        |

| LPDDR                | Single end    | 1.8              | Yes        | No        |

| PCI33                | Single end    | 3.3              | Yes        | No        |

| VREF1_DRIVER         | Single end    | 1.8/1.2/1.35/1.5 | No         | Yes       |

# 3.3.2 I/O Logic

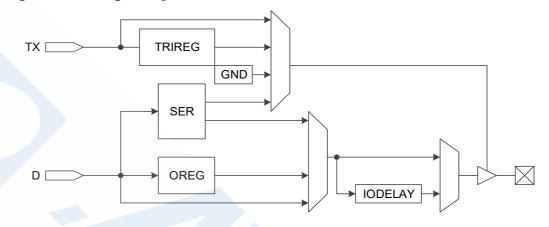

Figure 3-7 shows the I/O logic output of Arora V series of FPGA Products.

Figure 3-7 I/O Logic Output

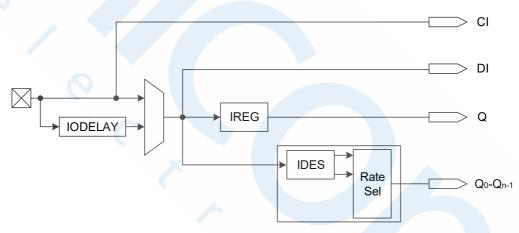

Figure 3-8 shows the I/O logic input of the Arora V series of FPGA Products.

Figure 3-8 I/O Logic Input

**Table 3-3 Port Description**

| Port Name         | I/O    | Description                                                                                             |  |  |  |

|-------------------|--------|---------------------------------------------------------------------------------------------------------|--|--|--|

| CI <sup>[1]</sup> | Input  | GCLK Input Signal<br>For the number of GCLK input signals, refer to<br><u>UG982, GW5AT-138 Pinout</u> . |  |  |  |

| DI                | Input  | IO port low-speed input signal, entering into Fabric directly.                                          |  |  |  |

| Q                 | Output | IREG output signal in SDR module.                                                                       |  |  |  |

| Q0-Qn-1           | Output | IDES output signal in DDR module.                                                                       |  |  |  |

Note!

When CI is used as GCLK input, DI, Q, and  $Q_0\mathchar`-Q_{n\mathchar`-1}$  cannot be used as I/O input and output.

Descriptions of the I/O logic modules of Arora V series of FPGA Products are presented below.

## **Delay Module**

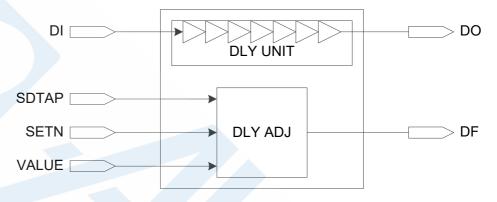

See Figure 3-9 for an overview of the IODELAY. Each I/O of Arora V includes IODELAY, providing a total of 128 (0~127) delays, with a single-step delay time of about 18ps.

#### Figure 3-9 IODELAY

There are three ways to control the delay cell:

- Static control.

- Dynamic control: can be realized by combing the integrated logic circuit.

- Adaptive control

#### I/O Register

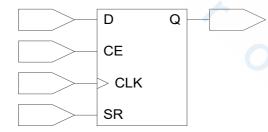

See Figure 3-10 for the I/O register in Arora V series of FPGA Products. Each I/O provides one input register (IREG), one output register (OREG), and a tristate Register (TREG).

Figure 3-10 Register Structure in I/O Logic

#### Note!

- CE can be either active low (0: enable) or active high (1: enable).

- CLK can be either rising edge trigger or falling edge trigger.

- SR can be either synchronous/asynchronous SET or RESET or disable.

- The register can be programmed as DFF or latch.

## **De-serializer DES and Clock Domain Transfer**

The Arora V series of FPGA Products provide a simple De-serializer DES for each input I/O to support advanced I/O protocols. The clock domain transfers module of the input clock in DES provides the ability to safely switch the external sampling clock to the internal continuous running clock. There are multiple registers used for data sampling.

The clock domain transfer module offers the following functions:

- The internal continuous clock is used instead of the discontinuous DQS for data sampling. The function is applied to the interface of DDR memory.

- For the DDR3 memory interface standard, align the data after DQS read-leveling.

- In regular DDR mode, when DQS.RCLK is used for sampling, clock domain transfer module also needs to be used.

Each DQS provides WADDR and RADDR signals to the same group in the clock domain transfer module.

## Serializer SER

The Arora V series of FPGA Products provide a simple Serializer SER for each output I/O to support advanced I/O protocols.

#### IDES and OSER

The Arora V series of FPGA Products support serialization and deserialization of various ratios, as shown in the following table:

Table 3-4 Serialization and deserialization ratio modes supported by The Arora V series of FPGA Products

| IOL type   | ratio modes supported                                                        |

|------------|------------------------------------------------------------------------------|

| IOL single | IDES: SDR/ 1:2/ 1:4/ 1:7/ 1:8/ 1:10/ 1:14/1:16<br>OSER: SDR/2:1/4:1/7:1/8:1/ |

| IOL pair   | IDES: 1:32<br>OSER: 10:1/16:1/14:1 <sup>[1]</sup>                            |

Note!

14:1 OSER is only supported on GW5A-25.

# 3.3.3 I/O Logic Modes

The I/O Logic in Arora V series of FPGA Products supports several modes. In each operation, the I/O (or I/O differential pair) can be configured as output, input, and INOUT or tristate output (output signal with tristate control).

For more details, see UG304, Arora V series Programmable Input/Output (GPIO) User Guide.

# 3.4 Block SRAM (BSRAM)

# 3.4.1 Introduction

Arora V series of FPGA Products provide abundant SRAM. The Block SRAM (BSRAM) is embedded as a row in the FPGA array. Therefore, it is called block static random memory (BSRAM). Up to 36Kbits can be configured for each BSRAM. There are five operation modes: Single Port, Dual Port, Semi Dual Port, Semi Dual Port with ECC function, and ROM modes.

An abundance of BSRAM resources provide a guarantee for the user's high-performance design. BSRAM features:

- Max.36Kbits per BSRAM

- BSRAM itself can run at 380MHz at max (typical, Read-before-write is 230MHz)

- Support Single Port Mode

- Support Dual Port Mode

- Support Semi Dual Port Mode

- Supports ECC detection and error correction Function

- Support ROM Mode

- Data width up to 72bits

- Dual Port and Semi Dual Port support independent read/write clock and independent data width

- Read Mode supports register output or bypass output

- Write Mode supports Normal Mode, read-before-write Mode, writethrough Mode

# 3.4.2 Configuration Mode

The BSRAM mode in the Arora V series of FPGA Products supports different data bus widths. See Table 3-5.

| Capacity | Single Port<br>Mode | Dual Port<br>Mode | Semi Dual<br>Port Mode | Semi Dual Port<br>with ECC function | Read<br>Only |

|----------|---------------------|-------------------|------------------------|-------------------------------------|--------------|

|          | 16K x 1             | 16K x 1           | 16K x 1                | -                                   | 16K x 1      |

|          | 8K x 2              | 8K x 2            | 8K x 2                 | _                                   | 8K x 2       |

| 16Khita  | 4K x 4              | 4K x 4            | 4K x 4                 | -                                   | 4K x 4       |

| 16Kbits  | 2K x 8              | 2K x 8            | 2K x 8                 | -                                   | 2K x 8       |

|          | 1K x 16             | 1K x 16           | 1K x 16                | -                                   | 1K x 16      |

|          | 512 x 32            | _                 | 512 x 32               | -                                   | 512 x 32     |

| 19Khita  | 2K x 9              | 2K x 9            | 2K x 9                 | -                                   | 2K x 9       |

| 18Kbits  | 1K x 18             | 1K x 18           | 1K x 18                | -                                   | 1K x 18      |

Table 3-5 Memory Size Configuration

| Capacity | Single Port<br>Mode | Dual Port<br>Mode | Semi Dual<br>Port Mode | Semi Dual Port<br>with ECC function | Read<br>Only |

|----------|---------------------|-------------------|------------------------|-------------------------------------|--------------|

|          | 512 x 36            | -                 | 512 x 36               | _                                   | 512 x 36     |

| 26Khita  | _                   | _                 | _                      | 1K x 36                             | _            |

| 36Kbits  | _                   | _                 | _                      | 512 x 72                            | _            |

#### Single Port Mode

In the single port mode, BSRAM can write to or read from one port at one clock edge. Normal-Write Mode and Write-through Mode can be supported. In Normal-Write Mode, the written data will be stored in the internal memory array. In Write-through Mode, the written data will not only be stored in the internal memory array, but also be written to the output of BSRAM. When the output register is bypassed, the new data will show at the same write clock rising edge.

For further description of the block diagram and related description in single port mode, please refer to *UG300, Arora V* series BSRAM & SSRAM User Guide.

## **Dual Port Mode**

BSRAM supports Dual Port mode. The applicable operations are as follows:

- Two independent read, reading data from any given address.

- Two independent write, writing data to any address that is different.

- An independent read and an independent write at different clock frequencies.

#### Note!

- In Dual-port mode, Port A and Port B can read from or write to the same address. Null or repeated reads do not damage the storage module.

- In Dual-port mode, when Port A and Port B write to the same address at the same time, the dual ports writing fail at the same time.

- When Port A reads, Port B writes, and they access the same address, the write port succeeds, but the read port fails, and the output data is unknown. BSRAM contents are the values from the write port.

Dual Port supports independent read/write clocks and independent read/write data width. For further description of the block diagram and

related description in dual port mode, please refer to UG300, Arora V series BSRAM & SSRAM User Guide.

#### Semi Dual Port Mode

Semi-dual ports support independent read/write operations in the form of A port write-only ("normal write mode") and B port read-only. When Port A reads, Port B writes, and they access the same address, the write port succeeds, but the read port fails, and the output data is unknown. BSRAM contents are the values from the write port.

Semi-dual Port supports independent read/write clocks and independent read/write data width. For further description of the block

diagram and related description in semi-dual port mode, please refer to *UG300, Arora V series BSRAM & SSRAM User Guide*.

## Semi Dual Port Mode with ECC Function

Semi-dual ports with ECC Function support independent read/write operations in the form of A port write-only ("normal write mode") and B port read-only. This mode supports ECC error detection and correction. For further details, please refer to *UG300, Arora V* series BSRAM & SSRAM User Guide.

## **Read Only**

BSRAM can be configured as ROM. The ROM can be initialized during the device configuration stage, and the ROM data needs to be provided in the initialization file. Initialization completes during the device power-on process.

Each BSRAM can be configured as one 16 Kbits ROM. For further description of the block diagram and details description in ROM mode, please refer to *UG300, Arora V* series BSRAM & SSRAM User Guide.

# 3.4.3 Data Bus Width Configuration

The BSRAM in the Arora V series of FPGA products supports independent data bus width of write/read operation. In the Dual Port, Semi Dual Port, Semi Dual Port with ECC function modes, the data bus width for read and write can be different. For the data width supported by Port A and Port B, see Table 3-6, Table 3-7, and Table 3-8.

| Consoity | Apacity Port B |         |        |        |        |         |        |         |  |

|----------|----------------|---------|--------|--------|--------|---------|--------|---------|--|

| Capacity | FOILB          | 16K x 1 | 8K x 2 | 4K x 4 | 2K x 8 | 1K x 16 | 2K x 9 | 1K x 18 |  |

|          | 16K x 1        | *       | *      | *      | *      | *       | N/A    | N/A     |  |

|          | 8K x 2         | *       | *      | *      | *      | *       | N/A    | N/A     |  |

| 16Kbits  | 4K x 4         | *       | *      | *      | *      | *       | N/A    | N/A     |  |

|          | 2K x 8         | *       | *      | *      | *      | *       | N/A    | N/A     |  |

|          | 1K x 16        | *       | *      | *      | *      | *       | N/A    | N/A     |  |

| 18Kbits  | 2K x 9         | N/A     | N/A    | N/A    | N/A    | N/A     | *      | *       |  |

| TORDILS  | 1K x 18        | N/A     | N/A    | N/A    | N/A    | N/A     | *      | *       |  |

#### Table 3-6 Read/Write Data Width Configuration in Dual Port Mode

Table 3-7 Read/Write Data Width Configuration in Semi Dual Port Mode

| Port A   |         |            |           |           |           |            |            | 0         |           |             |            |             |

|----------|---------|------------|-----------|-----------|-----------|------------|------------|-----------|-----------|-------------|------------|-------------|

| Capacity | Port B  | 16K<br>x 1 | 8K x<br>2 | 4K x<br>4 | 2K x<br>8 | 1K x<br>16 | 512x<br>32 | 2K x<br>9 | 1K<br>x18 | 512<br>x 36 | 1K x<br>36 | 512<br>x 72 |

|          | 16K x 1 | *          | *         | *         | *         | *          | *          | N/A       | N/A       | N/A         | N/A        | N/A         |

| 16Kbits  | 8K x 2  | *          | *         | *         | *         | *          | *          | N/A       | N/A       | N/A         | N/A        | N/A         |

|          | 4K x 4  | *          | *         | *         | *         | *          | *          | N/A       | N/A       | N/A         | N/A        | N/A         |

|          | Port A   |            |           |           |           |            |            |           |           |             |            |             |

|----------|----------|------------|-----------|-----------|-----------|------------|------------|-----------|-----------|-------------|------------|-------------|

| Capacity | Port B   | 16K<br>x 1 | 8K x<br>2 | 4K x<br>4 | 2K x<br>8 | 1K x<br>16 | 512x<br>32 | 2K x<br>9 | 1K<br>x18 | 512<br>x 36 | 1K x<br>36 | 512<br>x 72 |

|          | 2K x 8   | *          | *         | *         | *         | *          | *          | N/A       | N/A       | N/A         | N/A        | N/A         |

|          | 1K x 16  | *          | *         | *         | *         | *          | *          | N/A       | N/A       | N/A         | N/A        | N/A         |

|          | 512 x 32 | *          | *         | *         | *         | *          | *          | N/A       | N/A       | N/A         | N/A        | N/A         |

| 18Kbits  | 2K x 9   | N/A        | N/A       | N/A       | N/A       | N/A        | N/A        | *         | *         | *           | N/A        | N/A         |

| TORDILS  | 1K x 18  | N/A        | N/A       | N/A       | N/A       | N/A        | N/A        | *         | *         | *           | N/A        | N/A         |

# Table 3-8 Read/Write Data Width Configuration in Semi Dual Port with ECC Function Mode

| Capacity | Port B   | Port A  |          |

|----------|----------|---------|----------|

| Capacity | POILD    | 1K x 36 | 512 x 72 |

| 26Khita  | 1K x 36  | *       | N/A      |

| 36Kbits  | 512 x 72 | N/A     | *        |

# 3.4.4 ECC (GW5A(T)-138)

The BSRAM of Arora V series GW5A(T)-138 FPGA products has a built-in ECC hardcore module, which is mainly used for data detection and correction during data transfer and storage. The features as follows:

- Supports ECC error detection and correction in SDP 512 x 64 and SDP 1024 x 36 modes only;

- Supports 1-bit error correction and 2-bit error alarm in 64-bit SRAM data;

- 72-bit ECC module contains 64-bit data bits and 8-bit parity bits;

- Support 1-bit and 2-bit error injection for bit 31 and bit 63.

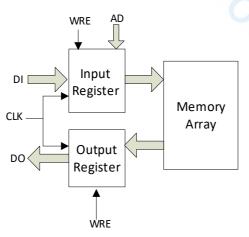

# 3.4.5 Byte-enable

The BSRAM in the Arora V series of FPGA Products supports byteenable. For data longer than a byte, the additional bits can be blocked, and only the selected portion can be written into. The byte-enable function can only be used for writing and is available when the data width is 16/18, 32/36 bits. The blocked bits will be retained for future operation. Read/write enable ports (WREA, WREB), and byte parameter options can be used to control the BSRAM write operation.

# 3.4.6 Synchronous Operation

- All the input registers of BSRAM support synchronous write.

- The output register can be used as a pipeline register to improve design performance.

- The output registers are bypass-able.

# 3.4.7 Power up Conditions

BSRAM initialization is supported when powering up. During the power-up process, BSRAM is in standby mode, and all the data outputs are "0". This also applies in ROM mode.

# 3.4.8 BSRAM Operation Modes

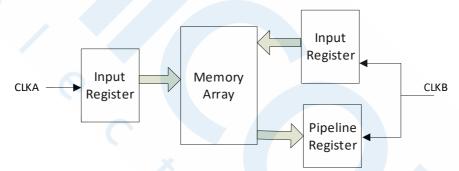

BSRAM supports five different operations, including two read operations (Bypass Mode and Pipeline Read Mode) and three write operations (Normal Write Mode, Write-through Mode, and read-beforewrite Mode).

## **Read Mode**

Read data from the BSRAM via output registers or without using the registers.

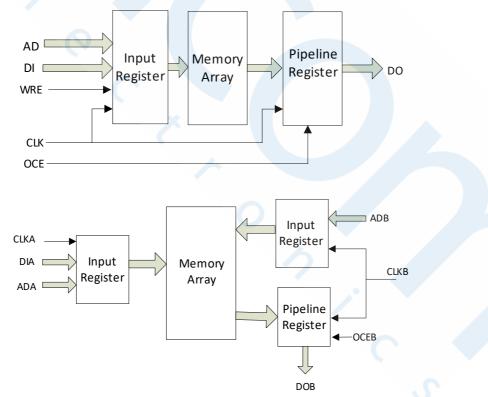

## **Pipeline Mode**

When reading data, the data is synchronously read out via the output register according to the clock beat. This mode supports up to 72-bit data width.

## **Bypass Mode**

The output register is not used. When reading data, the data is directly sent to the output port.

Figure 3-11 Pipeline Mode in Single Port, Dual Port and Semi-Dual Port

## Write Mode

## Normal Write Mode

In this mode, when the user writes data to one port, and the output data of this port does not change. The data written in will not appear at the read port.

## Write-through Mode

In this mode, when the user writes data to one port, and the data written in will also appear at the output of this port.

#### **Read-before-write Mode**

In this mode, when the user writes data to one port, and the data written in will be stored in the memory according to the address. The original data in this address will appear at the output of this port.

# 3.4.9 Clock Operations

Table 3-9 lists the clock operations in different BSRAM modes:

Table 3-9 Clock Operations in Different BSRAM Modes

| Clock                     | BSRAM Mode     |                     |                  |  |  |  |  |  |

|---------------------------|----------------|---------------------|------------------|--|--|--|--|--|

| Operations                | Dual Port Mode | Semi-Dual Port Mode | Single Port Mode |  |  |  |  |  |

| Independent<br>Clock Mode | Yes            | No                  | No               |  |  |  |  |  |

| Read/Write<br>Clock Mode  | Yes            | Yes                 | No               |  |  |  |  |  |

| Single Port<br>Clock Mode | No             | No                  | Yes              |  |  |  |  |  |

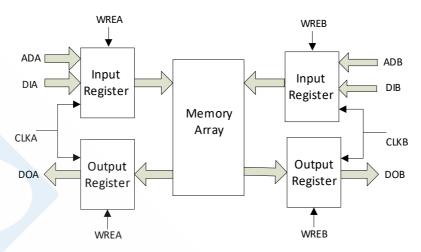

## Independent Clock Mode

Figure 3-12 shows the independent clocks in dual port mode with each port with one clock. CLKA controls all the registers at Port A; CLKB controls all the registers at Port B.

#### Figure 3-12 Independent Clock Mode

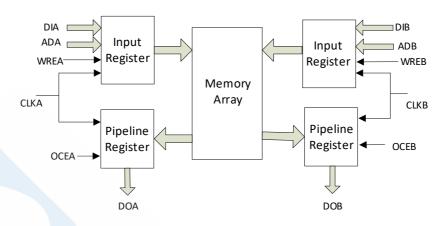

**Read/Write Clock Operation**

Figure 3-13 shows the read/write clock operations in the semi-dual port mode with one clock at each port. The write clock (CLKA) controls Port A data inputs, write address and read/write enable signals. The read clock (CLKB) controls Port B data output, read address, and read enable signals.

Figure 3-13 Read/Write Clock Mode

## Single Port Clock Mode

Figure 3-14 shows the clock operation in single port mode.

Figure 3-14 Single Port Clock Mode

# 3.5 DSP

Arora V series of FPGA Products integrate brand new DSP modules. Gowin DSP solutions can meet user demands for high performance digital signal processing design, such as FIR, FFT, etc. DSP blocks have the advantages of stable timing performance, high-usage, and low-power.

The DSP features are as follows:

- Can be configured as 12 x 12, 27 x 28, and 27 x 36 signed multipliers

- 48-bit ALU

- Multipliers cascading to support wider data

- Barrel Shifter

- Adaptive filtering through signal feedback

- Supports pipeline mode and bypass mode

- Data is operated by signs

- All operands for arithmetic operation are signed numbers Each DSP consists of three stages:

- Input multiplexer and input registers

- One pre-adder, two multipliers, and pipeline registers

- ALU, output multiplexers, and output registers

# 3.5.1 PADD

Each DSP features one PADD(pre-adder) to implement pre-add, presubtraction, and shifting.

PADD locates at the first stage with two inputs:

- 26-bit input C

- Parallel 26-bit input A or SIA

Each input end supports pipeline mode and bypass mode.

# 3.5.2 MULT

Each DSP has one 27 x 18 multiplier M0 and one 12 x 12 multiplier M1, locating after the pre-adder, which can further enhance MULT's functions. Registered Mode and Bypass Mode are supported both in input and output ports.

Multiplier M0 can be configured as:

- One 27 x 18 multiplier

- One 12 x 12 multiplier

- Two DSPs can form a 27 x 36 multiplier

Multiplier M1 can only be configured as one 12 x 12 multiplier.

When multiplier M0 and multiplier M1 are configured as both 12 x 12

multipliers and the ALU is enabled, 12 x 12SUM mode can be achieved.

# 3.5.3 ALU

Each Macro has one four-input 48-bit ALU, which can further enhance MULT's functions. The registered and bypass mode are supported both in input and output ports. The 56-bit ALU supports multiplier M0 output, multiplier M1 output (or 48bit operand D), ALU cascade input, and ALU output feedback or addition/subtraction operations of static PRE LOAD value.

# 3.5.4 Operating Mode

Based on control signals, DSP can be configured as different operation modes. Operation Modes:

- Multiplier

- Accumulator

- MULTADDALU

For further detailed information about the DSP, please refer to *UG305, Arora V series DSP User Guide*.

# 3.6 Gigabit Transceivers (GW5AT-138)

Gowin Arora V series of FPGA Products(GW5AT-138) support two Transceiver Quads. Each Quad supports up to four transceivers, and each transceiver is comprised of one TX and one RX, with the data rate raging from 270Mbps to 12.5Gbps, and supports flexible PMA and PCS. The structure View is as shown in Figure 3-15. The protocols supported are as follows:

- PCI Express, V2.0 (2.5 Gbps /5.0 Gbps)

- 10 Gigabit Attachment Unit Interface (XAUI) (3.125Gbps)

- RXAUI (Reduced XAUI) (6.25Gbps)

- CEI-6G-SR (6.375Gbps)

- SATA Rev3.2 (6Gbps/3Gbps/1.5Gbps) (need soft IP support)

- Serial GMII(SGMII) (1.25Gbps)

- CPRI (need soft IP support; soft IP available)

- JESD204B (need soft IP support; soft IP available)

- Rapid-IO (need soft IP support; soft IP available)

- 1000Base-X (need soft IP support; soft IP available)

- 10G-Base-R (need soft IP support; soft IP available)

- SDI-Tx/Rx (need soft IP support; soft IP available)

- SLVS-EC(Rx) (need soft IP support; soft IP available)

Figure 3-15 Gigabit Transceiver Architecture View

| Bank 0                             |                                    |                        |                                    |                                    | Bank 1                             |                                    |                        |                                    |                                    |

|------------------------------------|------------------------------------|------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------|------------------------------------|------------------------------------|

| CH0 PMA<br>TX + RX                 | CH1 PMA<br>TX + RX                 | Quad 0<br>Common Logic | CH2 PMA<br>TX + RX                 | CH3 PMA<br>TX + RX                 | CH0 PMA<br>TX + RX                 | CH1 PMA<br>TX + RX                 | Quad 1<br>Common Logic | CH2 PMA<br>TX + RX                 | CH3 PMA<br>TX + RX                 |

| CH0 PCS<br>PCIe PCS + Flexible PCS | CH1 PCS<br>PCIe PCS + Flexible PCS |                        | CH2 PCS<br>PCIe PCS + Flexible PCS | CH3 PCS<br>PCIe PCS + Flexible PCS | CH0 PCS<br>PCIe PCS + Flexible PCS | CH1 PCS<br>PCIe PCS + Flexible PCS |                        | CH2 PCS<br>PCIe PCS + Flexible PCS | CH3 PCS<br>PCIe PCS + Flexible PCS |

| FPGA Fabric                        |                                    |                        |                                    |                                    |                                    |                                    |                        |                                    |                                    |

# Physical Medium Attachment (PMA)

- Two shared PLLs per Quad (one is LC PLL and the other is ring oscillator PLL).

- Transmitter through tracking of spread reference clock.

- Lane driver with programmable transmitter equalization with 1 tap precursor and 1 tap post-cursor to improve signal integrity.

- Voltage mode/current mode lane driver with board AC coupling.

- Programmable continuous time linear equalizer (CTLE) with autoadaption.

- Receiver CDR track SSC data and tolerance +/- 5000ppm variation.

- Beacon signaling generation and detection for PCI Express.

#### **Physical Coding Sublayer (PCS)**

- Dedicated hard PCIe PCS

- Flexible PCS to support PCS customization

- 8b/10b encoder/decoder

- Supports TX channel bonding

- Supports RX channel bonding and CTC

- Utilize IF FIFO to simply user system design

- Supports flexible parallel data widths of 8/10/16/20/32/40/64/80 bits

For further detailed information about Gowin Gigabit Transceiver, please refer to UG299, Arora V series Gigabit Transceiver User Guide.

# 3.7 PCIe 2.0 (GW5AT-138)

GW5AT-138 FPGA Products include one integrated block for PCI Express technology. It allows custom FPGA-to-FPGA communication via the PCI Express protocol, and to attach ASSP Endpoint devices, such as Ethernet Controllers or Fiber Channel HBAs (Host Bus Adapter), to the FPGA.

Features of the PCIe integrated block are as follows:

- Dedicated hard core IP, Compliant to the PCI Express Base Specification 2.0

- Supports x1, x2, x4, x8 lanes

- Supports Root Complex port and End Point

- Supports Gen1 (2.5Gb/s), Gen2 (5Gb/s)

- Up to six BARs, resizable

- Lane reversal

- Receiver supports polarity inversion

- Supports CrossLink connection mode

- Supports Multicast

- Supports ARI (Alternative Routing-ID Interpretation)

- Supports IDO (ID-based Ordering)

- Retimer (extension device) presence detection

- Supports TPH (TLP Processing Hints)

- Supports ACS (Access Control Services)

- Supports DPC (Downstream Port Containment)

- Supports PTM (Precision Time Measurement)

- Supports Autonomous link speed/width change

- Supports advanced configuration options, Advanced Error Reporting (AER), and End-to-End Cyclic Redundancy Check (ECRC)

- Configurable parameters: channel width, maximum payload size, FPGA logical interface speeds, reference clock frequency, base address register decoding and filtering, etc.

For more details on PCIe 2.0, please refer to UG298, Arora V series Hardened PCIe Controller User Guide.

# 3.8 MIPI D-PHY

#### 3.8.1 MIPI D-PHY RX (GW5A(T)-138)

GW5A(T)-138 FPGA Products provide a MIPI D-PHY RX hardcore supporting MIPI Alliance Standard for D-PHY Specification V1.2. The dedicated D-PHY core supports MIPI DSI and CSI-2 mobile video interfaces for cameras and displays. The main features of the MIPI D-PHY RX hardcore are as follows:

- High Speed RX at up to 20 Gbps (eight data channels).

- One Bank supports up to four data lanes and one clock lane. Up to two banks supported.

- Bidirectional Low-power (LP) mode at up to 10Mbps per lane

- Built-in HS Sync, bit and lane alignment

- 1:8 and 1:16 deserialization modes to FPGA fabric's user interface

- Supports MIPI DSI and MIPI CSI-2 link layers

For further detailed information on Gowin MIPI D-PHY RX/TX, pleae refer to *UG296, Arora V series Hardened MIPI D-PHY RX User Guide.*

#### 3.8.2 MIPI D-PHY RX/TX(GW5A-25)

GW5A-25 FPGA Products provide a MIPI D-PHY RX/TX hardcore supporting MIPI Alliance Standard for D-PHY Specification V1.2. The dedicated D-PHY core supports MIPI DSI (Display Serial Interface) and CSI-2 (Camera Serial Interface) mobile video interfaces for cameras and displays. The main features of the MIPI D-PHY RX/TX hardcore are as follows:

- High Speed RX/TX up to 10 Gbps with four data lanes.

- Supports up to four data lanes and one clock lane.

- Bidirectional Low-power (LP) mode at up to 10Mbps per lane

- Built-in HS Sync, bit and lane alignment

- 1:8 and 1:16 deserialization modes to FPGA fabric's user interface

Supports MIPI DSI and MIPI CSI-2 link layers

For further detailed information on Gowin MIPI D-PHY RX/TX, pleae refer to *UG296*, Arora V series Hardened MIPI D-PHY RX User Guide.

# 3.9 Analog to Digital Converter (ADC)

Arora V integrates a new flexible analog interface as temperature and power sensor. When combined with the programmable logic capability of the FPGA, the sensor can address the data acquisition and monitoring requirements for temperature and power monitoring.

Highlights of the sensor architecture include:

- On-chip reference, no off-chip voltage reference required

- 60dB SNR

- 10-bit oversampling @ 2MHz

- 1kHz Signal Bandwidth

- two dedicated analog channels, able to detect input signals from GPIO at the same time

- On-chip temperature (±4°C max error) and power supply (±1% max error) sensors

- Continuous access to ADC measurements

The sensor optionally uses an on-chip reference circuit  $(\pm 1\%)$ , thereby eliminating the need for any external active components for basic on-chip monitoring of temperature and power supply rails.

The most recent measurement results (together with maximum and minimum readings) are stored in dedicated registers for access at any time via the user interface.

For further detailed information about ADC, please refer to UG299, Arora V series ADC User Guide.

# 3.10 Clock

The clock resources and wiring are critical for high-performance applications in FPGA. Arora V series of FPGA Products provide the global clock network (GCLK) which connects to all the registers directly. Besides GCLK, clock resources such as PLL, high speed clock HCLK, DDR memory interface, and DQS, etc are also provided.

Please refer to  $3.10.1 \sim 3.10.4$  for a brief introduction. For further detailed information on the GCLK, HCLK, DDR memory interface, and DQS, please refer to *UG306, Arora V series Clock User Guide*.

#### 3.10.1 Global Clock