## Features

- ADC Performance:

- Analog Multiplexer with 8-full Differential or 16single Ended Inputs

- Programmable Amplifier Programmable Gain: 1 to 128

- Low Noise: nV<sub>RMS</sub>

- Programmable Data Rates: 2.5 SPS to 8 kSPS

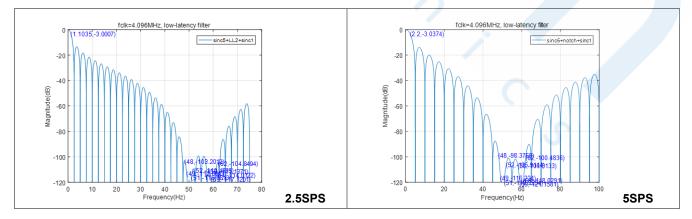

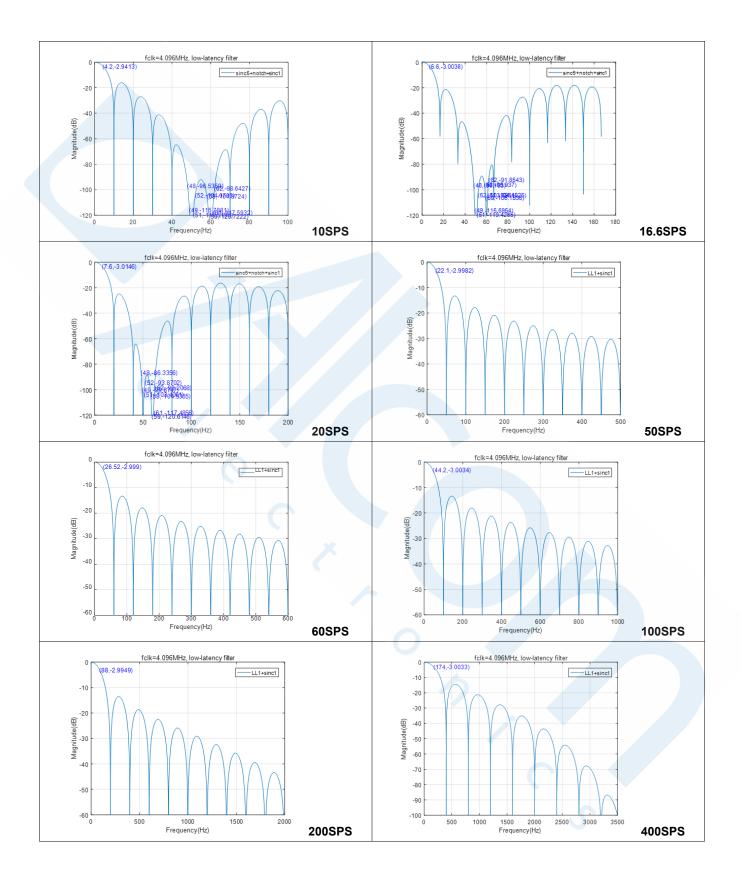

- Digital Filter: Simultaneous 50-Hz and 60-Hz Rejection at ≤ 20 SPS with Low-Latency Digital Filter

- Integrated Functions:

- Dual-Matched Programmable Current Sources for Sensor Excitation: 10 μA to 2000 μA

- Internal Reference: 2.5 V

- Internal Oscillator

- Internal Temperature Sensor

- Extended Fault Detection Circuits

- Self Offset and System Calibration

- GPIO and GPO pins with external mux control

- Digital Interface

- 3-/4- wire SPI-Compatible Interface with CRC Checking

- Digital Supply: 2.7 V to 5 V

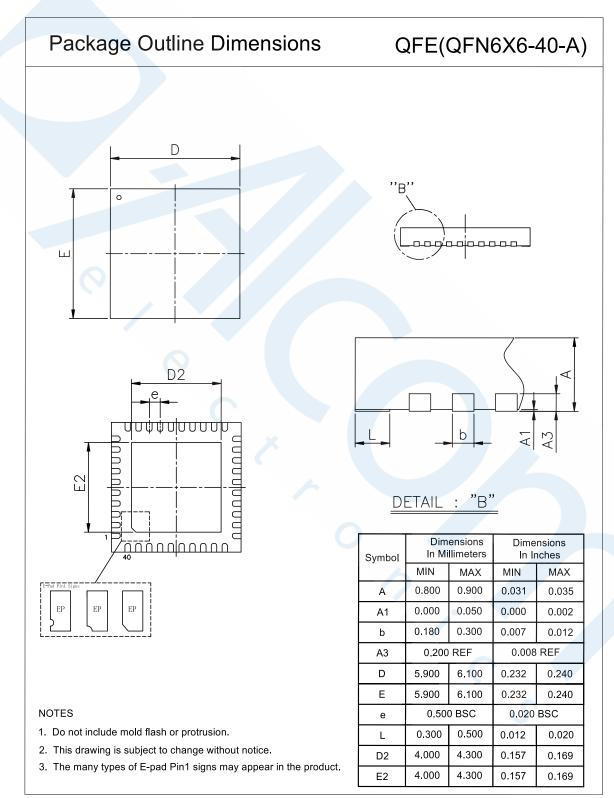

- Package: 40-lead 6mm x 6 mm QFN

- Operating Temperature: -40°C to +125°C

## Applications

- Process Control: PLC/DCS Modules

- Voltage, Current, Temperature, and Pressure Measurement Flow Meters

- Temperature Controllers

- Medical and Scientific Instrumentation

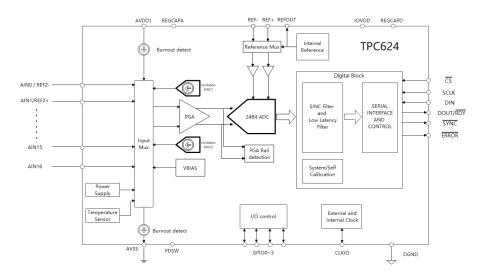

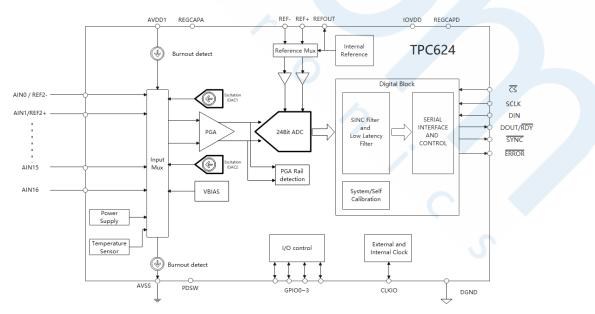

## Description

TPC6240 is a precision 8-/16-channel, multiplexed ADC with integrated PGA and many other features, offering accurate measurement for low-bandwidth input signals, and lower-system cost and component count.

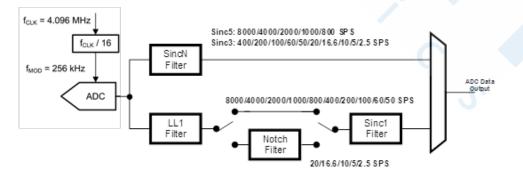

The device has a 24-bit delta-sigma converter, with configurable data rates. There are sinc5 filter for optimized nosie performance, and low-latency filter for fast settling with 50-/60-Hz rejection for noisy industrial environments.

A low-noise programmable gain amplifer provides 1~128 gain options to amplify low-level signals.

Additionaly, it integrates a precision 2.5-V band gap reference and integrated oscillator.

Two programmable exitation current souces are available for easy RTD biasing for temperature measurement.

Finally, more features such as burn out, CRC, voltage bias, system monitoring, and GPIOs are integrated.

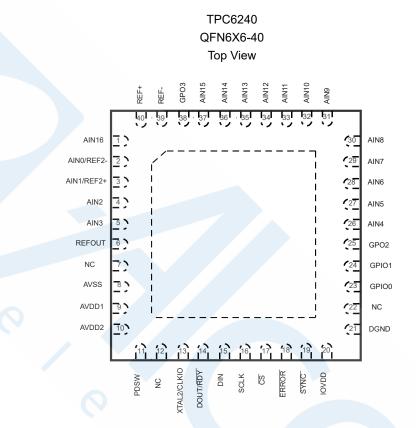

The device is available in QFN6X6-40 package.

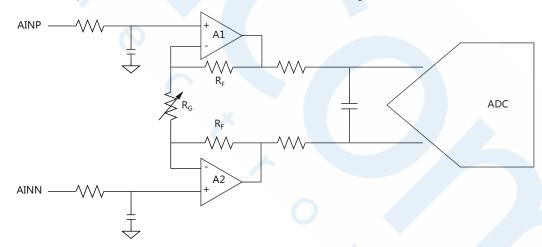

## **Typical Application Circuit**

## **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Product Family Table                    | 3  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          |    |

| Absolute Maximum Ratings <sup>(1)</sup> |    |

| ESD, Electrostatic Discharge Protection | 7  |

| Recommended Operating Conditions        | 7  |

| Thermal Information                     | 8  |

| Electrical Characteristics              | 9  |

| Timing Requirements                     | 13 |

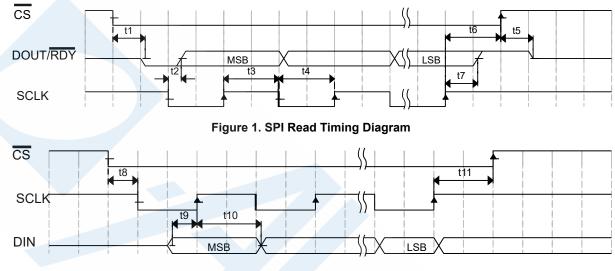

| Timing Diagrams                         | 14 |

| Noise Performance                       | 14 |

| Detailed Description                    | 24 |

| Overview                                | 24 |

| Functional Block Diagram                | 24 |

| Feature Description                     | 25 |

| Device Functional Modes                 | 37 |

| Serial Interface                        | 39 |

| Register Table                          | 41 |

| Application and Implementation          | 70 |

| Application Information                 | 70 |

| Layout                                  | 71 |

| Layout Guideline                        | 71 |

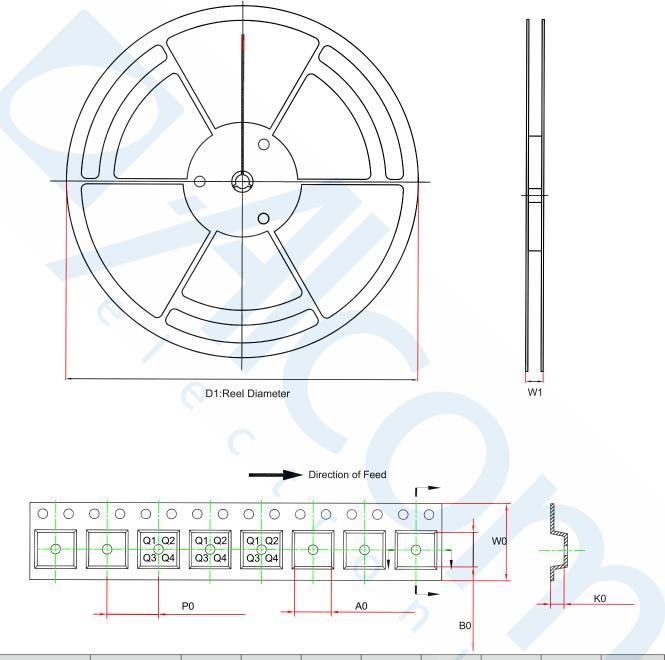

| Tape and Reel Information               |    |

| Package Outline Dimensions              | 73 |

| QFN6X6-40                               |    |

| Order Information                       | 74 |

| IMPORTANT NOTICE AND DISCLAIMER         | 75 |

|                                         |    |

# Product Family Table

| Order Number   | ADC resolution | ADC channel | Temperature Range | Package   |

|----------------|----------------|-------------|-------------------|-----------|

| TPC6240-QFER-S | 24             | 16          | −40°C to 125°C    | QFN6X6-40 |

# **Revision History**

| Date       | Revision | Notes             |

|------------|----------|-------------------|

| 2023-07-18 | Rev.A.0  | Released Version. |

# **Pin Configuration and Functions**

### Table 1. Pin Functions: TPC6240

| PIN No. | Mnemonic   | Туре | Description                                                                                                                                                                                                                                                                                                 |  |

|---------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       |            | AI   | Analog Input. Selectable through cross point mux.                                                                                                                                                                                                                                                           |  |

| 2       | AIN0/REF2- | AI   | Analog Input 0 (AIN0)/Reference 2, Negative Input (REF2-). An external reference can be applied between REF2+ and REF2 REF2- can span from AVSS to AVDD1-1V. Analog Input 0 is selectable through cross point mux. Reference 2 can be selected through the REFSEL bits in the setup configuration register. |  |

| 3       | AIN1/REF2+ | AI   | Analog Input 1 (AIN0)/Reference 2, Positive Input (REF2+). An external reference can be applied between REF2+ and REF2 REF2+ can span from AVDD1 to AVSS+1V. Analog Input 1 is selectable through cross point mux. Reference 2 can be selected through the REFSEL bits in the setup configuration register. |  |

| 4       | AIN2       | AI   | Analog Input. Selectable through cross point mux.                                                                                                                                                                                                                                                           |  |

| 5       | AIN3       | AI   | Analog Input. Selectable through cross point mux.                                                                                                                                                                                                                                                           |  |

| 6       | REFOUT     | AO   | Buffered Output of Internal Reference. The output is 2.5 V with respect to AVSS.                                                                                                                                                                                                                            |  |

| 7       | NC         | NC   |                                                                                                                                                                                                                                                                                                             |  |

| 8       | AVSS       | Р    | Negative Analog Supply. This supply ranges from 0 V to -2.75 V and is nominally set to 0 V.                                                                                                                                                                                                                 |  |

| PIN No. | Mnemonic | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9       | AVDD1    | Р    | Analog Supply Voltage 1. This voltage ranges from 3.0 V minimum to 5.5 V maximum with respect to AVSS.                                                                                                                                                                                                                                                                                                                                                                                    |

| 10      | AVDD2    | Р    | Analog Supply Voltage 2. This voltage should be connected with AVDD1 together.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11      | PDSW     | AO   | Power-Down Switch Connected to AVSS. This pin is controlled by the PDSW bit in the GPIOCON register.                                                                                                                                                                                                                                                                                                                                                                                      |

| 12      | NC       | NC   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13      | CLKIO    | DIO  | Input 2 for Crystal (XTAL2)/Clock Input or Output (CLKIO). See the CLOCKSEL bit settings in the ADCMODE register (Table 25) for more information.                                                                                                                                                                                                                                                                                                                                         |

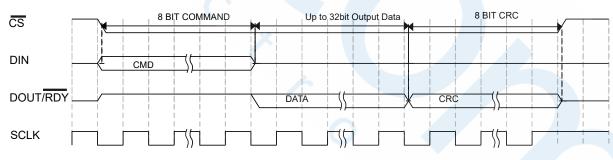

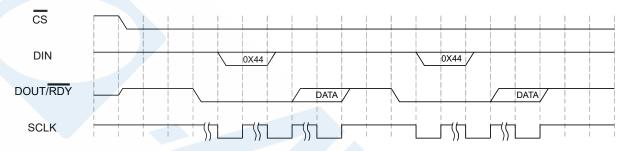

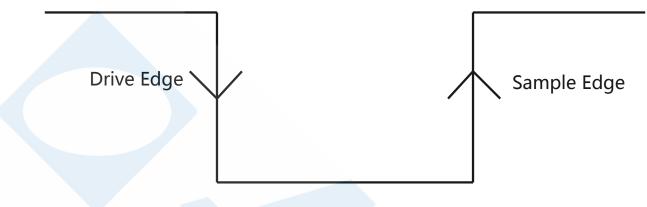

|         |          |      | Serial Data Output (DOUT)/Data Ready Output ( $\overline{RDY}$ ). This pin serves a dual purpose. It functions as a serial data output pin to access the output shift register of the ADC. The output shift register can contain data from any of the on-chip data or control registers. The data-word/control word information is placed on the DOUT/ $\overline{RDY}$ pin on the SCLK falling edge and is valid on the SCLK rising                                                      |

| 14      | DOUT/RDY | DO   | edge. When $\overline{CS}$ is high, the DOUT/ $\overline{RDY}$ output is tristated. When $\overline{CS}$ is low, and a register is not being read, DOUT/ $\overline{RDY}$ operates as a data ready pin, going low to indicate the completion of a conversion. If the data is not read after the conversion, the pin goes high before the next update occurs. The DOUT/ $\overline{RDY}$ falling edge can be used as an interrupt to a processor, indicating that valid data is available. |

| 15      | DIN      | DI   | Serial Data Input to the Input Shift Register on the ADC. Data in this shift register is transferred to the control registers in the ADC, with the register address (RA) bits of the communications register identifying the appropriate register. Data is clocked in on the rising edge of SCLK.                                                                                                                                                                                         |

| 16      | SCLK     | DI   | Serial Clock Input. This serial clock input is for data transfers to and from the ADC. SCLK has a Schmitt trigger input, making the interface suitable for opto-<br>isolated applications                                                                                                                                                                                                                                                                                                 |

| 17      | CS       | DI   | Chip Select Input. This is an active low logic input used to select the ADC. $\overline{CS}$ can be used to select the ADC in systems with more than one device on the serial bus. $\overline{CS}$ can be hardwired low, allowing the ADC to operate in 3-wire mode with SCLK, DIN, and DOUT used to interface with the device. When $\overline{CS}$ is high, the DOUT/ $\overline{RDY}$ output is tristated.                                                                             |

|         |          |      | This pin can be used in one of the following three modes:                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |          |      | Active low error input mode. This mode sets the ADC_ERROR bit in the STATUS register.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18      | ERROR    | DI/O | Active low, open-drain error output mode. The STATUS register error bits are mapped to the ERROR pin. The ERROR pins of multiple devices can be wired together to a common pull-up resistor so that an error on any device can be observed.                                                                                                                                                                                                                                               |

|         |          |      | General-purpose output mode. The status of the pin is controlled by the ERR_DAT bit in the GPIOCON register. The pin is referenced between IOVDD and DGND, as opposed to the AVDD1 and AVSS levels used by the GPIO1 and GPIO2 pins. The ERROR pin has an active pull-up in this case.                                                                                                                                                                                                    |

| PIN No. | Mnemonic | Туре | Description                                                                                                                                                                                                                                                                 |

|---------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19      | SYNC     | DI   | Synchronization Input. Allows synchronization of the digital filters and analog modulators when using multiple devices.                                                                                                                                                     |

| 20      | IOVDD    | Ρ    | Digital I/O Supply Voltage. IOVDD voltage ranges from 2 V to 5 V. IOVDD is independent of AVDD1 and AVDD2. For example, IOVDD can be operated at 3.3 V when AVDD1 or AVDD2 equals 5 V, or vice versa. If AVSS is set to -2.5 V, the voltage on IOVDD must not exceed 3.6 V. |

| 21      | DGND     | Р    | Digital Ground.                                                                                                                                                                                                                                                             |

| 22      | NC       | NC   |                                                                                                                                                                                                                                                                             |

| 23      | GPI00    | DI/O | General-Purpose Input/Output. Logic input/output on this this pin is referred to the AVDD1 and AVSS supplies.                                                                                                                                                               |

| 24      | GPIO1    | DI/O | General-Purpose Input/Output. Logic input/output on this this pin is referred to the AVDD1 and AVSS supplies.                                                                                                                                                               |

| 25      | GPO2     | DO   | General-Purpose Output. Logic output on this this pin is referred to the AVDD1 and AVSS supplies.                                                                                                                                                                           |

| 26      | AIN4     | AI   |                                                                                                                                                                                                                                                                             |

| 27      | AIN5     | AI   |                                                                                                                                                                                                                                                                             |

| 28      | AIN6     | AI   |                                                                                                                                                                                                                                                                             |

| 29      | AIN7     | AI   |                                                                                                                                                                                                                                                                             |

| 30      | AIN8     | AI   |                                                                                                                                                                                                                                                                             |

| 31      | AIN9     | AI   | Analog Input Selectable through cross point muy                                                                                                                                                                                                                             |

| 32      | AIN10    | AI   | Analog Input. Selectable through cross point mux.                                                                                                                                                                                                                           |

| 33      | AIN11    | AI   |                                                                                                                                                                                                                                                                             |

| 34      | AIN12    | AI   |                                                                                                                                                                                                                                                                             |

| 35      | AIN13    | AI   |                                                                                                                                                                                                                                                                             |

| 36      | AIN14    | AI   |                                                                                                                                                                                                                                                                             |

| 37      | AIN15    | AI   |                                                                                                                                                                                                                                                                             |

| 38      | GPO3     | DO   | General-Purpose Output. Logic output on this this pin is referred to the AVDD1 and AVSS supplies.                                                                                                                                                                           |

| 39      | REF-     | AI   | Reference 1 Input Negative Terminal. REF- can span from AVSS to AVDD1-1<br>V. Reference 1 can be selected through the REFSEL bits in the SETUP<br>CONFIGURATION register.                                                                                                   |

| 40      | REF+     | AI   | Reference 1 Input Positive Terminal. An external reference can be applied<br>between REF+ and REF REF+ can span from AVDD1 to AVSS + 1 V. Reference<br>1 can be selected through the REFSEL bits in the SETUP CONFIGURATION<br>register.                                    |

|         | EP       | Р    | Exposed Pad. The exposed pad should be soldered to a similar pad on the PCB under the exposed paddle to confer mechanical strength to the package and for heat dissipation. The exposed pad must be connected to AVSS through this pad on the PCB.                          |

## **Specifications**

## Absolute Maximum Ratings <sup>(1)</sup>

|                   |                                      | Min   | Max         | Unit |

|-------------------|--------------------------------------|-------|-------------|------|

|                   | AVDD1 to AVSS                        | -0.3  | 6.5         | V    |

|                   | AVDD1 to DGND                        | -0.3  | 6.5         | V    |

| Supply<br>Voltage | IOVDD to AVSS                        | -0.3  | 6.5         | V    |

| voltage           | IOVDD to DGND                        | -0.3  | 6.5         | V    |

|                   | AVSS to DGND                         | -3.25 | 0.3         | V    |

|                   | Analog Input to AVSS                 | -0.3  | AVDD1 + 0.3 | V    |

|                   | Reference Input to AVSS              | -0.3  | AVDD1 + 0.3 | V    |

| Input/Output      | GPIO to AVSS                         | -0.3  | AVDD1 + 0.3 | V    |

| Pin               | Digital Input to DGND                | -0.3  | IOVDD + 0.3 | V    |

|                   | Digital Output to DGND               | -0.3  | IOVDD + 0.3 | V    |

|                   | Analog and Digital Pin Input Current | -10   | 10          | mA   |

|                   | Operating Temperature Range          | -40   | 125         | °C   |

| Temperature       | Maximum Junction Temperature         | -40   | 150         | °C   |

|                   | Storage Temperature Range            | -65   | 150         | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### ESD, Electrostatic Discharge Protection

| Symbol | Parameter                | Condition                  | Minimum Level | Unit |

|--------|--------------------------|----------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | 2             | kV   |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | 1             | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

|         | Parameter                | Test Conditions | Min         | Тур | Мах         | Units |  |  |

|---------|--------------------------|-----------------|-------------|-----|-------------|-------|--|--|

| Power S | Power Supply             |                 |             |     |             |       |  |  |

|         |                          | AVDD to AVSS    | 3           | C   | 5.5         | V     |  |  |

| AVDD    | AVDD Analog Power Supply | AVSS to DGND    | -2.5        | 0   | 0           | V     |  |  |

|         |                          | AVDD to DGND    | 1.5         |     | 5.5         | V     |  |  |

| D) (D D |                          | IOVDD to DGND   | 2           |     | 5.5         | V     |  |  |

| DVDD    | Digital Power Supply     | IOVDD to AVSS   | 2           |     | 8           | V     |  |  |

| VAIN    | Absolute input voltage   | PGA bypass      | AVSS - 0.05 |     | AVDD + 0.05 | V     |  |  |

|            | Parameter                              | Test Conditions             | Min           | Тур   | Max         | Units |

|------------|----------------------------------------|-----------------------------|---------------|-------|-------------|-------|

|            |                                        | PGA enabled, Gain = 1-8     | AV (00 + 0.4F |       |             | V     |

|            |                                        | PGA enabled, Gain =16 ~ 128 | AVSS + 0.15   |       | AVDD - 0.35 | V     |

| VIN        | Differential input voltage             | VIN = VAINP - VAINN         | -VREF/Gain    |       | VREF/Gain   | V     |

| Voltage R  | eference Input                         |                             |               |       |             |       |

| VREF       | Absolute differential input<br>Voltage |                             | 1             |       | AVDD - AVSS | V     |

|            | Absolute negative reference            | REF BUF Bypass              | AVSS          |       | VREFP - 1   | V     |

| VREFN      | Voltage                                | REF BUF Enable              | AVSS + 0.5    |       | VREFP - 1   | V     |

| VOEEED     | Absolute positive reference            | REF BUF Bypass              | VREFN + 1     |       | AVDD + 0.05 | V     |

| VRFEFP     | Voltage                                | REF BUF Enable              | VREFN + 1     |       | AVDD - 0.5  | V     |

| External   | Clock Source                           |                             |               |       |             |       |

|            | external clock frequency               |                             | 2             | 4.096 | 4.5         | MHz   |

|            | duty cycle                             |                             | 40            | 50    | 60          | %     |

| Internal C | lock Source                            |                             |               |       |             |       |

|            | Clock frequency                        |                             |               | 4.096 |             | MHz   |

|            | Accuracy                               |                             | -2            |       | 2           | %     |

| General F  | Purpose Inputs                         |                             |               |       |             |       |

|            | GPIO Input Voltage                     |                             | AVSS - 0.05   |       | AVDD + 0.05 | V     |

| Digital In | outs                                   |                             |               |       |             |       |

|            | Digital Input Voltage                  |                             | DGND          |       | IOVDD       | V     |

| Temperat   | ure Range                              |                             |               |       |             |       |

| TJ         | Operating junction temperature         |                             | -40           |       | 125         | °C    |

### **Thermal Information**

| Package Type | θ <sub>JA</sub> | θις | Unit |

|--------------|-----------------|-----|------|

| QFN6X6-40    | 114             |     | °C/W |

### **Electrical Characteristics**

All minimum/maximum specifications at  $T_J = -40^{\circ}$ C to +125°C and all typical specifications at  $T_J = 25^{\circ}$ C, VDD = 3.0 V to 5.5 V, IOVDD = 1.65 V to 5.5 V, VSS = 0 V, unless otherwise noted.

| Parameter                                       | Test Conditions                              | Min                                   | Тур           | Max   | Units              |

|-------------------------------------------------|----------------------------------------------|---------------------------------------|---------------|-------|--------------------|

| Analog Input                                    |                                              |                                       |               |       |                    |

|                                                 | PGA bypassed                                 |                                       | 20            |       | nA                 |

| Absolute Input Current                          | PGA enabled                                  |                                       | 0.1           |       | nA                 |

|                                                 | PGA bypassed                                 |                                       | 2             |       | pA/°C              |

| absolute Input Current Drift                    | PGA enabled                                  |                                       | 2             |       | pA/°C              |

|                                                 | VCM = AVDD/2, PGA bypassed                   |                                       | 1             |       | nA/V               |

| Differential Input Current                      | VCM = AVDD/2, PGA enabled                    |                                       | 2             |       | nA                 |

|                                                 | VCM = AVDD/2, PGA bypassed                   |                                       | 20            |       | pA/°C              |

| Differential Input Current Drift                | VCM = AVDD/2, PGA enabled                    |                                       | 20            |       | pA/°C              |

| System Performance                              |                                              |                                       |               |       |                    |

| Resolution                                      |                                              | 24                                    |               |       | bit                |

| Data Rate                                       |                                              | 2.5                                   |               | 4k/8k | SPS                |

|                                                 | PGA bypassed                                 |                                       | 3             |       | ppm <sub>FSR</sub> |

| INL(best fit)                                   | PGA gain = 1~8                               |                                       | 5             |       | ppm <sub>FSR</sub> |

|                                                 | PGA gain = 16~128                            |                                       | 10            |       | ppm <sub>FSR</sub> |

|                                                 | PGA bypassed                                 | -180                                  |               | 180   | μV                 |

|                                                 | PGA bypassed, after internal vos calibration | on the order of noisepp at the set DR |               |       |                    |

|                                                 | PGA bypassed, Global chop                    | -3.5                                  | 0.2           | 3.5   | μV                 |

| Input Offset Voltage                            | PGA gain = 1                                 |                                       | ±180          |       | μV                 |

|                                                 | PGA gain = 2~8                               |                                       | ±180/<br>GAIN |       | μV                 |

|                                                 | PGA gain = 16-128                            |                                       | 15            |       | μV                 |

|                                                 | PGA bypassed                                 |                                       | 200           |       | nV/°C              |

|                                                 | PGA Gain = 1~8                               | 5                                     | 100           |       | nV/°C              |

| Offset Drift                                    | PGA Gain = 16~128                            |                                       | 20            |       | nV/°C              |

|                                                 | PGA bypassed or enable, Global chop          | 1                                     | 5             |       | nV/°C              |

|                                                 | PGA bypassed                                 | -450                                  | 0             | 450   | ppm                |

|                                                 | PGA Gain = 1                                 | -500                                  |               | 500   | ppm                |

| Gain Error<br>(Exclude Voltage Reference Error) | PGA Gain = 2                                 | -900                                  |               | 900   | ppm                |

| (Exclude voltage Relefence Error)               | PGA Gain = 4                                 | -1300                                 |               | 1300  | ppm                |

|                                                 | PGA Gain = 8~128                             | -1700                                 |               | 1700  | ppm                |

| Gain Drift                                      | PGA bypassed                                 |                                       | 0.5           |       | ppm/°C             |

| Parameter                         | Test Conditions                            | Min   | Тур                                                         | Max      | Units             |

|-----------------------------------|--------------------------------------------|-------|-------------------------------------------------------------|----------|-------------------|

| (Exclude Voltage Reference Error) | PGA Gain = 1~128                           |       | 1                                                           |          | ppm/°C            |

| Noise (inout referred)            | PGA Gain = 128, DR = 2.5SPS,<br>sinc3      |       | 25                                                          |          | nV <sub>RMS</sub> |

| CMRR                              | at dc ,PGA on                              |       | 115                                                         |          | dB                |

| PSRR                              | AVDD at dc,PGA on                          |       | 90                                                          |          | dB                |

| Voltage Reference inputs          |                                            |       |                                                             |          |                   |

| Absolute Input Current            | Ref buffer disabled, ext VREF = 2.5<br>V   |       | 5                                                           |          | uA/V              |

|                                   | Ref buffer enabled, ext VREF = 2.5 V       |       | 2                                                           |          | uA/V              |

| Internal Voltage Reference        |                                            |       |                                                             |          |                   |

| Output Voltage                    |                                            |       | 2.5                                                         |          | V                 |

| Accuracy                          | TA = 25°C                                  | ±0.1% |                                                             | ±0.1%    | %                 |

| Temperature Drift                 | -40~125°C                                  |       | 20                                                          |          | ppm/°C            |

|                                   | (AVDD = 3.0~3.3)                           | -5    |                                                             | 5        | mA                |

| Output Current                    | (AVDD = 3.3~5.5)                           | -10   |                                                             | 10       | mA                |

| Short-circuit Llimit Current      | sink or source                             |       | 50                                                          |          | mA                |

| PSRR                              | AVDD at dc                                 |       | 85                                                          |          | dB                |

|                                   | AVDD = 2.7~3.3 (3.0~3.3),<br>IL=-5~5 mA    |       | 60                                                          |          | µV/mA             |

| Load Regulation                   | AVDD = 3.3~5.25 (3.3~5.5),<br>IL=-10~10 mA |       | 60                                                          |          | µV/mA             |

| Startup Time                      | 1 μF cap, 0.001% settling                  |       | 5                                                           |          | ms                |

| Capacitive Load Stability         | ×                                          | 1     |                                                             | 47       | μF                |

| Reference Noise                   | 0.1~10 Hz, 1 µF сар                        |       | 12                                                          |          | μV <sub>PP</sub>  |

| Excitation Current Sources (IDACs | ;)                                         |       |                                                             |          |                   |

| Current Setting                   | 0                                          |       | 10, 50,<br>100, 250,<br>500, 750,<br>1000,<br>1500,<br>2000 |          | μΑ                |

| Compliance Valtage                | 10 μA~750 μA, 0.1% deviation               | AVSS  |                                                             | AVDD-0.4 | V                 |

| Compliance Voltage                | 1 mA~2 mA, 0.1% deviation                  | AVSS  |                                                             | AVDD-0.6 | V                 |

| Accuracy (each IDAC)              | 10 μA to 100 μA                            | -5    | 0.7                                                         | 5        | %                 |

| $T_A = 25^{\circ}C$               | 250 μA to 2 mA                             | -3    | 0.5                                                         | 3        | %                 |

|                                   | 10 μA to 100 μA                            |       | 0.15                                                        | 0.8      | %                 |

| Current Mismatch betwewn IDACs    | 250 μA to 750 μA                           |       | 0.1                                                         | 0.6      | %                 |

| $T_A = 25^{\circ}C$               | 1 mA to 2 mA                               |       | 0.07                                                        | 0.4      | %                 |

| Temperature Drift (each IDAC)     | 10 μA to 750 μA                            |       | 20                                                          |          | ppm/°C            |

| Parameter                                 | Test Conditions     | Min           | Тур                   | Мах           | Units  |

|-------------------------------------------|---------------------|---------------|-----------------------|---------------|--------|

|                                           | 1 m to 2 mA         |               | 10                    |               | ppm/°C |

| Temperature Drift Matching between        | 10 μA to 100 μA     |               | 3                     |               | ppm/°C |

| IDACs                                     | 250 μA to 2 mA      |               | 2                     |               | ppm/°C |

| Startup Time                              |                     |               | 25                    |               | μs     |

| BIAS Voltage                              |                     |               | 1                     |               |        |

| Output Voltage Settings                   |                     |               | VDD+AVSS<br>/DD+AVSS) |               | V      |

| Output Voltage Accuracy                   |                     |               |                       |               | %      |

| Output Impedance                          |                     |               | 800                   |               | Ω      |

| Startup Time                              | 1 μF, 0.1% settling |               | 2.8                   |               | ms     |

| Burnout Current Sources(BOCS)             |                     |               | 1                     |               |        |

| Current Setting                           |                     |               | 0.2, 1, 10            |               | μA     |

|                                           | 0.2 μΑ              |               | ±25                   |               | %      |

| Accuracy                                  | 1 μΑ                |               | ±4                    |               | %      |

|                                           | 10 µA               |               | ±2                    |               | %      |

| Reference Detection                       |                     |               |                       |               |        |

| Threshold 1                               |                     |               | 0.3                   |               | V      |

| Threshold 2                               |                     |               |                       |               | V      |

| Threshold 2 accuracy, T <sub>A</sub> = 25 |                     | -3            | ±1                    | 3             | %      |

| Pull-together Resistance                  |                     |               | 10                    |               | MΩ     |

| Temperature Sensor                        |                     | 1             |                       |               |        |

| Output Voltage                            | $T_A = 25^{\circ}C$ |               | 130                   |               | mV     |

| Temperature Coefficient                   |                     |               | 436                   |               | µV/°C  |

| Accuracy                                  |                     |               | ±2                    |               | °C     |

| Low-side Power Switch                     |                     |               |                       |               |        |

| On Resistance                             |                     |               | 3                     | 5             | Ω      |

| Current through Switch                    | 200 mV to AVSS      |               | 50                    |               | mA     |

| Digital Interface                         |                     |               |                       |               |        |

| VIH                                       |                     | 0.7*IOVD<br>D |                       | IOVDD         | V      |

| VIL                                       |                     | DGND          |                       | 0.3*IOVD<br>D | V      |

| V <sub>он</sub>                           |                     | 0.8*IOVD<br>D | C                     | IOVDD         | V      |

| VoL                                       |                     | DGND          |                       | 0.2*IOVD<br>D | V      |

| Input Current                             |                     |               | ±1                    |               | uA     |

| Power disspation                          |                     |               |                       | ·             |        |

| Parameter               | Test Conditions                            | Min            | Тур  | Max            | Units |

|-------------------------|--------------------------------------------|----------------|------|----------------|-------|

|                         | AVDD = 3 V                                 |                | 8.5  | 20             |       |

| AVDD, PD                | ADD = 5.5 V                                |                | 15   | 30             | uA    |

|                         | AVDD = 3 V                                 |                | 1.1  | 1.6            | •     |

| AVDD, Standby           | ADD = 5.5 V                                |                | 1.5  | 2.1            | mA    |

|                         | AVDD = 3 V, GAIN = -2                      |                | 1.1  | 1.7            |       |

|                         | AVDD = 3 V, GAIN = 8                       |                | 1.15 | 1.8            |       |

|                         | AVDD = 3 V, GAIN = 32                      |                | 1.25 | 1.9            |       |

|                         | AVDD = 3 V, GAIN = 128                     |                | 1.5  | 2.3            |       |

| AVDD, Norm Run          | AVDD = 5.5 V, GAIN = 2                     |                | 1.6  | 2.2            | mA    |

|                         | AVDD = 5.5 V, GAIN = 8                     |                | 1.65 | 2.3            |       |

|                         | AVDD = 5.5 V, GAIN = 32                    |                | 1.7  | 2.4            |       |

|                         | AVDD = 5.5 V, GAIN = 128                   |                | 2    | 2.8            |       |

|                         | IOVDD = 2 V                                |                | 9    | 70             |       |

| IODVDD, PD              | IOVDD = 5.5 V                              |                | 20   | 110            | uA    |

|                         | IOVDD = 2 V                                |                | 15   | 70             |       |

| IOVDD, Standby,Norm Run | IOVDD = 5.5 V                              |                | 40   | 110            | uA    |

| AVDD UVLO               |                                            |                | 2.4  |                | V     |

| GPIO                    |                                            |                |      |                |       |

| VIH                     |                                            | 0.7*VDD        |      | VDD+0.0<br>5   | V     |

| VIL                     |                                            | AVSS-0.0<br>5  |      | 0.3*VDD        | V     |

| Voн                     | IOH = 1 mA                                 | 0.8*VDD        |      | VDD            | V     |

| V <sub>OL</sub>         | IOL = 1 mA                                 | VSS            |      | 0.2*VDD        | V     |

| Io under Iovdd          |                                            |                |      |                |       |

|                         | 2 V < IOVDD < 2.3 V                        | 0.65*IOV<br>DD |      |                | V     |

| VIH                     | 2.3 V < IOVDD < 5.5 V                      | 0.7*IOVD<br>D  |      |                | v     |

| VIL                     | 2 V < IOVDD < 2.3 V                        |                |      | 0.35*IOV<br>DD | v     |

|                         | 2.3 V < IOVDD < 5.5 V                      |                |      | 0.7            | V     |

|                         | IOVDD > 4.5 V, Isource = 1 mA              | 0.8*IOVD<br>D  | C    |                | v     |

| V <sub>OH</sub>         | 2.7 V < IOVDD < 4.5 V, Isource = 0.5<br>mA | 0.8*IOVD<br>D  |      | S              | V     |

|                         | IOVDD < 2.7 V, Isource = 0.2 mA            | 0.8*IOVD<br>D  |      |                | V     |

| V <sub>OL</sub>         | IOVDD > 4.5 V, Isink = 2 mA                |                |      | 0.4            | V     |

| Parameter       | Test Conditions                          | Min | Тур | Мах | Units |

|-----------------|------------------------------------------|-----|-----|-----|-------|

|                 | 2.7 V < IOVDD < 4.5 V, Isource = 1<br>mA |     |     | 0.4 | V     |

|                 | IOVDD < 2.7 V, Isource=0.4mA             |     |     | 0.4 | V     |

| Leakage Current |                                          |     | ±10 |     | uA    |

### **Timing Requirements**

All minimum/maximum specifications at  $T_J = -40^{\circ}$ C to +125°C and all typical specifications at  $T_J = 25^{\circ}$ C, IOVDD = 2 V to 5.5 V, DOUT = 20 pF to DGND, unless otherwise noted.

| Parameter        |                 | Test Conditions/Comments                        | Min | Тур | Max | Unit |

|------------------|-----------------|-------------------------------------------------|-----|-----|-----|------|

| SCLK Pulse Width | t <sub>3</sub>  | SCLK high pulse width                           | 25  |     |     | ns   |

| SCLK Puise Width | t4              | SCLK low pulse width                            | 25  |     |     | ns   |

|                  |                 | CS falling edge to DOUT/RDY active time         | 0   |     |     | ns   |

|                  | t <sub>1</sub>  | IOVDD = 4.5 V to 5.5 V                          |     |     | 15  | ns   |

| 8                |                 | IOVDD = 2 V to 3.6 V                            |     |     | 40  | ns   |

|                  |                 | SCLK active edge to data valid delay            | 0   |     |     | ns   |

| Read Operation   | t <sub>2</sub>  | IOVDD = 4.5 V  to  5.5 V                        |     |     | 12  | ns   |

|                  | $\mathcal{C}$   | IOVDD = 2 V to 3.6 V                            |     |     | 25  | ns   |

|                  | t5              | Bus relinquish time after CS inactive edge      | 2.5 |     | 20  | ns   |

|                  | t <sub>6</sub>  | SCLK inactive edge to CS inactive edge          | 0   |     |     | ns   |

|                  | t7              | SCLK inactive edge to<br>DOUT/RDY high/low      | 10  |     |     | ns   |

|                  | t <sub>8</sub>  | CS falling edge to SCLK active edge setup time4 | 0   |     |     | ns   |

|                  | t <sub>9</sub>  | Data valid to SCLK edge setup time              | 8   |     |     | ns   |

| Write Operation  | t <sub>10</sub> | Data valid to SCLK edge hold<br>time            | 8   |     |     | ns   |

|                  | t <sub>11</sub> | CS rising edge to SCLK edge hold time           | 5   |     |     | ns   |

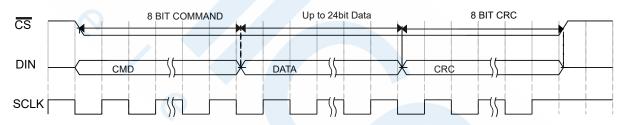

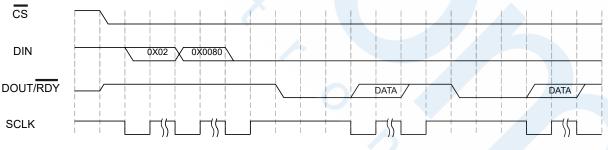

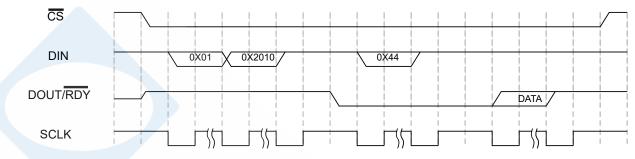

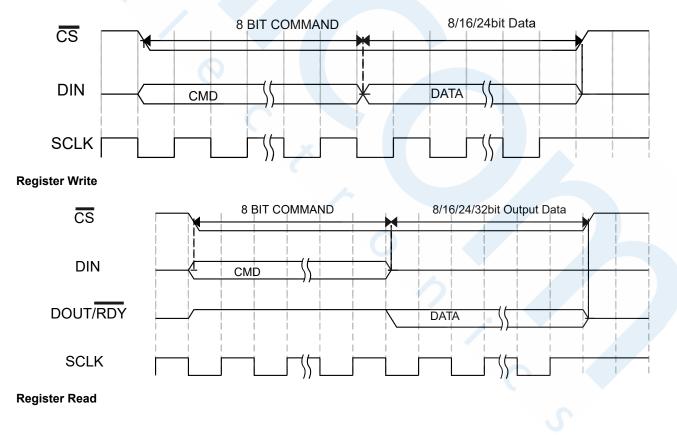

### Timing Diagrams

Figure 2. SPI Write Timing Diagram

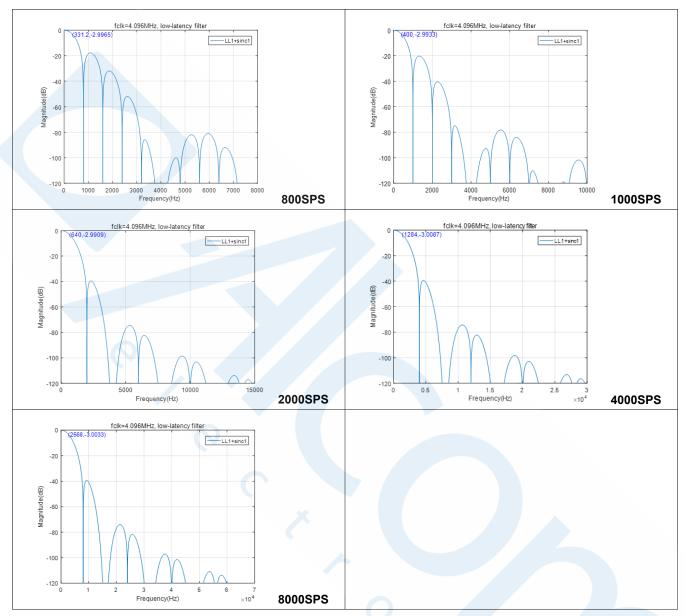

### **Noise Performance**

Delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converters (ADCs) are based on the principle of oversampling. The ratio between modulator frequency and output data rate is called the *oversampling ratio*(OSR). By increasing the OSR, and thus reducing the output data rate, the noise performance of the ADC can be optimized. In other words, the input-referred noise drops when reducing the output data rate because more samples of the internal modulator are averaged to yield one conversion result. Increasing the gain also reduces the input-referred noise, which is particularly useful when measuring low-level signals.

Use following equations to calculate effective resolution and noise-free resolution when using a reference voltage other than 2.5 V.

$\begin{array}{l} \mbox{Effective Resolution = ln[(2 \cdot V_{REF} / Gain) / V_{RMS-Noise}] / ln(2) \\ \mbox{Noise-Free Resolution= ln[(2 \cdot V_{REF} / Gain) / V_{PP-Noise}] / ln(2) \\ \end{array}$

(1) (2)

|          |        | SINC5  |        |        |         |         |         |          |         |  |  |  |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|--|--|--|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |  |  |  |

| 8000     | 26.98  | 34.35  | 44.15  | 39.90  | 64.25   | 109.29  | 204.84  | 357.03   | 31.96   |  |  |  |

| 4000     | 28.12  | 42.06  | 40.74  | 36.17  | 50.23   | 83.39   | 149.16  | 260.17   | 32.33   |  |  |  |

| 2000     | 18.03  | 16.59  | 17.83  | 21.60  | 30.97   | 59.57   | 104.06  | 180.89   | 15.32   |  |  |  |

| 1000     | 12.21  | 12.11  | 12.40  | 17.81  | 24.00   | 40.89   | 72.42   | 135.30   | 11.37   |  |  |  |

| 800      | 9.89   | 9.32   | 10.57  | 14.70  | 19.92   | 34.30   | 64.85   | 124.29   | 10.03   |  |  |  |

| 400      | 8.55   | 8.34   | 8.82   | 11.04  | 16.57   | 29.17   | 47.49   | 90.97    | 7.88    |  |  |  |

| 200      | 6.60   | 5.64   | 6.40   | 7.66   | 11.52   | 20.69   | 37.88   | 62.15    | 5.92    |  |  |  |

| 100      | 5.03   | 4.22   | 5.15   | 5.78   | 8.27    | 15.11   | 26.15   | 48.55    | 4.16    |  |  |  |

| 60       | 4.18   | 3.22   | 4.06   | 4.97   | 6.25    | 11.35   | 20.89   | 37.68    | 3.47    |  |  |  |

### Table 2. Noise in LSB<sub>RMS</sub> with Sinc<sup>5</sup>Filter, Global Chop Disabled, and Internal 2.5-V Reference

|          |        |        |        |        | SINC5   |         |         |          |         |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |

| 50       | 3.90   | 3.13   | 4.01   | 4.51   | 6.04    | 10.09   | 17.92   | 35.43    | 3.42    |

| 20       | 2.97   | 2.57   | 2.84   | 3.37   | 4.15    | 7.10    | 12.88   | 22.74    | 2.63    |

| 16       | 2.88   | 2.55   | 2.56   | 3.04   | 3.93    | 6.24    | 12.08   | 21.63    | 2.64    |

| 10       | 2.11   | 2.36   | 2.53   | 2.49   | 2.97    | 4.62    | 10.22   | 16.48    | 2.26    |

| 5        | 1.05   | 1.97   | 2.11   | 2.02   | 2.20    | 3.57    | 6.82    | 13.11    | 1.80    |

| 2.5      | 0.78   | 2.09   | 1.72   | 1.18   | 1.56    | 2.89    | 5.77    | 10.62    | 0.87    |

Table 3. Effective Resolution in RMS Noise with Sinc<sup>5</sup>Filter, Global Chop Disabled, and Internal 2.5-V Reference

|          |        |        |        |        | SINC5   |         |         |          |         |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |

| 8000     | 19.2   | 18.9   | 18.5   | 18.6   | 18.1    | 17.3    | 16.4    | 15.6     | 19.4    |

| 4000     | 19.2   | 19.0   | 18.9   | 18.9   | 18.5    | 17.8    | 16.9    | 16.0     | 19.2    |

| 2000     | 19.8   | 19.8   | 19.8   | 19.5   | 19.0    | 18.3    | 17.4    | 16.5     | 19.9    |

| 1000     | 20.4   | 20.4   | 20.3   | 20.0   | 19.6    | 18.7    | 18.0    | 17.1     | 20.5    |

| 800      | 20.7   | 20.5   | 20.4   | 20.2   | 19.7    | 18.9    | 18.0    | 17.2     | 20.7    |

| 400      | 20.9   | 20.8   | 20.8   | 20.6   | 20.1    | 19.3    | 18.3    | 17.4     | 20.9    |

| 200      | 21.3   | 21.3   | 21.2   | 20.9   | 20.5    | 19.8    | 18.9    | 18.0     | 21.3    |

| 100      | 21.7   | 21.7   | 21.6   | 21.4   | 21.0    | 20.2    | 19.4    | 18.4     | 21.7    |

| 60       | 21.9   | 21.9   | 21.8   | 21.7   | 21.4    | 20.6    | 19.7    | 18.9     | 21.9    |

| 50       | 22.0   | 22.0   | 21.9   | 21.9   | 21.5    | 20.7    | 19.9    | 18.9     | 22.0    |

| 20       | 22.4   | 22.3   | 22.3   | 22.3   | 22.2    | 21.4    | 20.5    | 19.6     | 22.4    |

| 16       | 22.5   | 22.3   | 22.4   | 22.5   | 22.3    | 21.4    | 20.6    | 19.8     | 22.5    |

| 10       | 22.9   | 22.5   | 22.5   | 22.9   | 22.7    | 21.9    | 20.9    | 20.1     | 23.0    |

| 5        | 23.9   | 22.7   | 22.9   | 23.5   | 23.1    | 22.3    | 21.6    | 20.6     | 24.0    |

| 2.5      | 24.4   | 23.4   | 23.7   | 24.0   | 23.6    | 22.9    | 22.0    | 21.0     | 24.4    |

Table 4. Noise in LSB<sub>pp</sub> with Sinc<sup>5</sup>Filter, Global Chop Disabled, and Internal 2.5-V Reference

|          | SINC5  |        |        |        |         |         |         |          |         |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |

| 8000     | 189    | 254    | 317    | 265    | 395     | 682     | 1222    | 2034     | 172     |

| 4000     | 195    | 230    | 234    | 230    | 298     | 553     | 859     | 1416     | 215     |

| 2000     | 117    | 104    | 109    | 149    | 199     | 343     | 740     | 1298     | 91      |

| 1000     | 71     | 77     | 84     | 106    | 124     | 248     | 446     | 874      | 67      |

| 800      | 67     | 75     | 69     | 80     | 120     | 203     | 395     | 647      | 59      |

| 400      | 58     | 62     | 56     | 69     | 95      | 151     | 320     | 710      | 53      |

|          | SINC5  |        |        |        |         |         |         |          |         |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |

| 200      | 45     | 41     | 41     | 56     | 77      | 120     | 219     | 398      | 42      |

| 100      | 29     | 31     | 28     | 39     | 56      | 94      | 150     | 311      | 30      |

| 60       | 26     | 30     | 25     | 31     | 38      | 69      | 125     | 217      | 25      |

| 50       | 22     | 22     | 26     | 27     | 36      | 69      | 116     | 231      | 22      |

| 20       | 17     | 19     | 17     | 21     | 23      | 39      | 66      | 137      | 19      |

| 16       | 17     | 18     | 18     | 17     | 21      | 36      | 67      | 111      | 15      |

| 10       | 11     | 16     | 15     | 12     | 15      | 32      | 52      | 98       | 10      |

| 5        | 6      | 11     | 10     | 9      | 12      | 22      | 36      | 69       | 7       |

| 2.5      | 4      | 7      | 6      | 6      | 9       | 14      | 25      | 45       | 4       |

# Table 5. Noise Free Resolution from Peak to Peak Noise with Sinc<sup>5</sup>Filter, Global Chop Disabled, and Internal 2.5-V Reference

|          |        |        |        |             | SINC5   |         |         |          |         |

|----------|--------|--------|--------|-------------|---------|---------|---------|----------|---------|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8      | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |

| 8000     | 16.4   | 16.0   | 15.7   | 16.0        | 15.4    | 14.6    | 13.7    | 13.0     | 16.6    |

| 4000     | 16.4   | 16.2   | 16.1   | 16.2        | 15.8    | 14.9    | 14.3    | 13.5     | 16.3    |

| 2000     | 17.1   | 17.3   | 17.2   | 16.8        | 16.4    | 15.6    | 14.5    | 13.7     | 17.5    |

| 1000     | 17.9   | 17.7   | 17.6   | 17.3        | 17.0    | 16.0    | 15.2    | 14.2     | 17.9    |

| 800      | 17.9   | 17.8   | 17.9   | 17.7        | 17.1    | 16.3    | 15.4    | 14.7     | 18.1    |

| 400      | 18.1   | 18.0   | 18.2   | 17.9        | 17.4    | 16.8    | 15.7    | 14.5     | 18.3    |

| 200      | 18.5   | 18.6   | 18.6   | 18.2        | 17.7    | 17.1    | 16.2    | 15.4     | 18.6    |

| 100      | 19.1   | 19.0   | 19.2   | <b>18.7</b> | 18.2    | 17.4    | 16.8    | 15.7     | 19.1    |

| 60       | 19.3   | 19.1   | 19.4   | 19.0        | 18.8    | 17.9    | 17.0    | 16.2     | 19.4    |

| 50       | 19.5   | 19.5   | 19.3   | 19.2        | 18.8    | 17.9    | 17.1    | 16.1     | 19.5    |

| 20       | 19.9   | 19.8   | 19.9   | 19.6        | 19.5    | 18.7    | 18.0    | 16.9     | 19.8    |

| 16       | 19.9   | 19.8   | 19.8   | 19.9        | 19.6    | 18.8    | 17.9    | 17.2     | 20.1    |

| 10       | 20.5   | 20.0   | 20.1   | 20.4        | 20.1    | 19.0    | 18.3    | 17.4     | 20.7    |

| 5        | 21.4   | 20.5   | 20.7   | 20.8        | 20.4    | 19.5    | 18.8    | 17.9     | 21.2    |

| 2.5      | 22.0   | 21.2   | 21.4   | 21.4        | 20.8    | 20.2    | 19.4    | 18.5     | 22.0    |

### Table 6. Noise in LSB<sub>RMS</sub>with Low Latency Filter, Global Chop Disabled, and Internal 2.5-V Reference

|          |        |        |        |        | LLF     |         |         |          |         |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |

| 8000     | 78.8   | 105.92 | 87.27  | 75.45  | 97.03   | 131.3   | 231.3   | 457.6    | 57.17   |

| 4000     | 93.47  | 95.1   | 103.09 | 97.36  | 76.83   | 112.8   | 224.2   | 382.6    | 91.19   |

| 2000     | 20.64  | 21.09  | 24.73  | 27.24  | 42.18   | 69.88   | 127.5   | 242.1    | 18.47   |

|          | LLF    |        |        |        |         |         |         |          |         |  |  |  |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|--|--|--|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |  |  |  |

| 1000     | 15.4   | 17.22  | 18.79  | 21.84  | 31.94   | 53.66   | 99.66   | 183.5    | 16.13   |  |  |  |

| 800      | 15.81  | 14.5   | 16.55  | 18.94  | 27.81   | 49.64   | 91.83   | 168.9    | 14.65   |  |  |  |

| 400      | 10.81  | 11.36  | 11.9   | 14.98  | 21.21   | 37.6    | 65.25   | 119.5    | 11      |  |  |  |

| 200      | 7.91   | 7.66   | 8.09   | 10.32  | 15.27   | 27.48   | 52.98   | 91.35    | 7.57    |  |  |  |

| 100      | 6.23   | 5.72   | 6.2    | 7.95   | 10.68   | 18.48   | 35.31   | 63.61    | 5.7     |  |  |  |

| 60       | 4.55   | 4.8    | 5.21   | 5.98   | 8.66    | 15.31   | 29.31   | 47.79    | 4.7     |  |  |  |

| 50       | 4.22   | 4.47   | 4.45   | 5.93   | 7.99    | 13.5    | 26.6    | 49.27    | 4.41    |  |  |  |

| 20       | 3.22   | 3.14   | 3.2    | 3.99   | 4.84    | 9.23    | 16.06   | 32.53    | 3.05    |  |  |  |

| 16       | 2.95   | 3.17   | 3.21   | 3.6    | 4.89    | 8.11    | 15.43   | 29.68    | 2.93    |  |  |  |

| 10       | 2.69   | 2.78   | 2.94   | 3.17   | 4.02    | 6.16    | 12.89   | 21.62    | 2.75    |  |  |  |

| 5        | 2.33   | 2.44   | 2.48   | 2.49   | 2.98    | 4.64    | 8.45    | 16.44    | 2.19    |  |  |  |

| 2.5      | 1.75   | 2.32   | 2.25   | 1.85   | 1.92    | 3.57    | 7.12    | 13.09    | 1.58    |  |  |  |

# Table 7. Effective resolution in RMS noise with Low Latency Filter, Global Chop Disabled, and Internal 2.5-V Reference

|          |        |        |        |              | LLF     |         |         |          |         |

|----------|--------|--------|--------|--------------|---------|---------|---------|----------|---------|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8       | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |

| 8000     | 18.9   | 17.8   | 17.3   | 17.6         | 17.7    | 17.0    | 16.1    | 15.2     | 18.7    |

| 4000     | 18.2   | 17.6   | 17.6   | 18.1         | 17.8    | 17.3    | 16.5    | 15.7     | 18.3    |

| 2000     | 19.6   | 19.5   | 19.5   | 19.2         | 18.7    | 17.9    | 17.1    | 16.1     | 19.7    |

| 1000     | 20.0   | 19.9   | 19.8   | 19.5         | 19.1    | 18.3    | 17.4    | 16.5     | 20.0    |

| 800      | 20.1   | 20.0   | 19.9   | <b>1</b> 9.7 | 19.2    | 18.4    | 17.5    | 16.7     | 20.1    |

| 400      | 20.5   | 20.4   | 20.4   | 20.1         | 19.7    | 18.9    | 18.0    | 17.1     | 20.6    |

| 200      | 20.9   | 21.0   | 20.9   | 20.5         | 20.1    | 19.3    | 18.5    | 17.5     | 20.9    |

| 100      | 21.4   | 21.4   | 21.3   | 21.0         | 20.6    | 19.8    | 19.0    | 18.0     | 21.3    |

| 60       | 21.7   | 21.6   | 21.5   | 21.4         | 21.0    | 20.2    | 19.3    | 18.5     | 21.6    |

| 50       | 21.7   | 21.7   | 21.7   | 21.5         | 21.1    | 20.3    | 19.4    | 18.6     | 21.7    |

| 20       | 22.1   | 22.1   | 22.1   | 22.0         | 21.7    | 20.9    | 20.1    | 19.2     | 22.1    |

| 16       | 22.2   | 22.2   | 22.2   | 22.1         | 21.9    | 21.1    | 20.2    | 19.4     | 22.2    |

| 10       | 22.4   | 22.4   | 22.3   | 22.4         | 22.3    | 21.5    | 20.6    | 19.6     | 22.5    |

| 5        | 23.2   | 22.5   | 22.6   | 23.1         | 22.7    | 22.0    | 21.1    | 20.2     | 23.2    |

| 2.5      | 23.9   | 22.8   | 23.0   | 23.6         | 23.1    | 22.4    | 21.5    | 20.7     | 23.8    |

|          |        |        |        |        | LLF     |         |         |          |         |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |

| 8000     | 223    | 578    | 793    | 642    | 473     | 829     | 1547    | 2774     | 397     |

| 4000     | 609    | 756    | 954    | 478    | 565     | 840     | 1335    | 2147     | 523     |

| 2000     | 138    | 151    | 153    | 209    | 241     | 398     | 708     | 1443     | 119     |

| 1000     | 115    | 110    | 115    | 127    | 213     | 291     | 638     | 1168     | 105     |

| 800      | 89     | 128    | 97     | 126    | 179     | 336     | 623     | 1069     | 97      |

| 400      | 67     | 74     | 72     | 103    | 120     | 220     | 484     | 799      | 68      |

| 200      | 57     | 55     | 58     | 67     | 92      | 169     | 274     | 647      | 60      |

| 100      | 32     | 37     | 45     | 48     | 62      | 108     | 214     | 438      | 36      |

| 60       | 31     | 38     | 40     | 38     | 55      | 87      | 166     | 287      | 34      |

| 50       | 31     | 29     | 29     | 39     | 51      | 81      | 142     | 267      | 28      |

| 20       | 19     | 23     | 21     | 26     | 35      | 54      | 97      | 189      | 22      |

| 16       | 21     | 19     | 19     | 24     | 29      | 55      | 107     | 174      | 20      |

| 10       | 16     | 16     | 17     | 18     | 20      | 36      | 67      | 128      | 17      |

| 5        | 9      | 15     | 13     | 13     | 17      | 24      | 42      | 79       | 10      |

| 2.5      | 7      | 12     | 10     | 8      | 12      | 18      | 38      | 65       | 8       |

### Table 8. Noise in LSB<sub>pp</sub>with Low Latency Filter, Global Chop Disabled, and Internal 2.5-V Reference

# Table 9. Noise Free Resolution from Peak to Peak noise with Low Latency Filter, Global Chop Disabled, and Internal 2.5-V Reference

|          |        |        | C.     |        | LLF     |         |         |          |         |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |

| 8000     | 16.2   | 14.8   | 14.4   | 14.7   | 15.1    | 14.3    | 13.4    | 12.6     | 15.4    |

| 4000     | 14.7   | 14.4   | 14.1   | 15.1   | 14.9    | 14.3    | 13.6    | 12.9     | 15.0    |

| 2000     | 16.9   | 16.8   | 16.7   | 16.3   | 16.1    | 15.4    | 14.5    | 13.5     | 17.1    |

| 1000     | 17.2   | 17.2   | 17.2   | 17.0   | 16.3    | 15.8    | 14.7    | 13.8     | 17.3    |

| 800      | 17.5   | 17.0   | 17.4   | 17.0   | 16.5    | 15.6    | 14.7    | 13.9     | 17.4    |

| 400      | 17.9   | 17.8   | 17.8   | 17.3   | 17.1    | 16.2    | 15.1    | 14.4     | 17.9    |

| 200      | 18.2   | 18.2   | 18.1   | 17.9   | 17.5    | 16.6    | 15.9    | 14.7     | 18.1    |

| 100      | 19.0   | 18.8   | 18.5   | 18.4   | 18.0    | 17.2    | 16.3    | 15.2     | 18.8    |

| 60       | 19.0   | 18.8   | 18.7   | 18.8   | 18.2    | 17.6    | 16.6    | 15.8     | 18.9    |

| 50       | 19.0   | 19.1   | 19.1   | 18.7   | 18.3    | 17.7    | 16.9    | 15.9     | 19.2    |

| 20       | 19.8   | 19.5   | 19.6   | 19.3   | 18.9    | 18.2    | 17.4    | 16.4     | 19.5    |

| 16       | 19.6   | 19.8   | 19.8   | 19.4   | 19.1    | 18.2    | 17.3    | 16.6     | 19.7    |

| 10       | 20.0   | 20.0   | 19.9   | 19.8   | 19.7    | 18.8    | 17.9    | 17.0     | 19.9    |

| 5        | 20.8   | 20.1   | 20.3   | 20.3   | 19.9    | 19.4    | 18.6    | 17.7     | 20.7    |

| 2.5      | 21.2   | 20.4   | 20.7   | 21.0   | 20.4    | 19.8    | 18.8    | 18.0     | 21.0    |

|          | SINC5  |        |        |        |         |         |         |          |         |  |  |  |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|--|--|--|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |  |  |  |

| 8000     | 25.00  | 42.49  | 43.10  | 60.40  | 48.27   | 81.85   | 149.72  | 281.31   | 45.47   |  |  |  |

| 4000     | 63.66  | 51.85  | 54.42  | 46.08  | 39.96   | 57.27   | 103.92  | 201.59   | 56.77   |  |  |  |

| 2000     | 12.33  | 12.85  | 14.71  | 15.64  | 23.20   | 40.35   | 77.98   | 133.62   | 12.16   |  |  |  |

| 1000     | 8.62   | 8.89   | 9.74   | 11.22  | 29.12   | 27.74   | 52.73   | 96.30    | 8.27    |  |  |  |

| 800      | 7.65   | 7.47   | 8.60   | 10.62  | 13.94   | 23.77   | 45.66   | 88.30    | 7.77    |  |  |  |

| 400      | 5.97   | 6.56   | 6.82   | 8.05   | 11.69   | 20.60   | 38.44   | 68.53    | 6.08    |  |  |  |

| 200      | 4.24   | 4.23   | 4.86   | 6.02   | 8.41    | 14.45   | 26.21   | 49.76    | 4.00    |  |  |  |

| 100      | 3.31   | 3.04   | 3.43   | 4.11   | 5.66    | 9.49    | 18.44   | 33.54    | 3.13    |  |  |  |

| 60       | 2.34   | 2.47   | 2.60   | 3.47   | 4.60    | 7.37    | 14.67   | 26.11    | 2.38    |  |  |  |

| 50 🧹     | 2.25   | 2.19   | 2.36   | 2.90   | 4.09    | 7.13    | 13.14   | 23.96    | 2.19    |  |  |  |

| 20       | 1.32   | 1.42   | 1.63   | 1.88   | 2.57    | 4.37    | 8.85    | 16.13    | 1.29    |  |  |  |

| 16       | 1.26   | 1.29   | 1.46   | 1.80   | 2.48    | 3.86    | 7.50    | 14.13    | 1.28    |  |  |  |

| 10       | 1.02   | 1.04   | 1.15   | 1.27   | 1.96    | 3.13    | 5.82    | 10.91    | 1.00    |  |  |  |

| 5        | 0.78   | 0.73   | 0.80   | 0.99   | 1.32    | 2.17    | 4.01    | 7.67     | 0.75    |  |  |  |

| 2.5      | 0.56   | 0.58   | 0.66   | 0.74   | 1.01    | 1.61    | 3.02    | 5.52     | 0.58    |  |  |  |

### Table 10. Noise in LSB<sub>RMS</sub> with Sinc<sup>5</sup>Filter, Global Chop Enabled, and Internal 2.5-V Reference

|          |        | SINC5  |        |        |         |         |         |          |         |  |  |  |  |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|--|--|--|--|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |  |  |  |  |

| 8000     | 19.4   | 18.6   | 18.6   | 18.1   | 18.4    | 17.6    | 16.8    | 15.9     | 18.5    |  |  |  |  |

| 4000     | 18.0   | 18.3   | 18.2   | 18.5   | 18.7    | 18.2    | 17.3    | 16.3     | 18.2    |  |  |  |  |

| 2000     | 20.4   | 20.3   | 20.1   | 20.0   | 19.5    | 18.7    | 17.7    | 16.9     | 20.4    |  |  |  |  |

| 1000     | 20.9   | 20.8   | 20.7   | 20.5   | 19.1    | 19.2    | 18.3    | 17.4     | 21.0    |  |  |  |  |

| 800      | 21.1   | 21.1   | 20.9   | 20.6   | 20.2    | 19.4    | 18.5    | 17.5     | 21.0    |  |  |  |  |

| 400      | 21.4   | 21.3   | 21.2   | 21.0   | 20.5    | 19.6    | 18.7    | 17.9     | 21.4    |  |  |  |  |

| 200      | 21.9   | 21.9   | 21.7   | 21.4   | 20.9    | 20.1    | 19.3    | 18.4     | 22.0    |  |  |  |  |

| 100      | 22.3   | 22.4   | 22.2   | 22.0   | 21.5    | 20.8    | 19.8    | 18.9     | 22.4    |  |  |  |  |

| 60       | 22.8   | 22.7   | 22.6   | 22.2   | 21.8    | 21.1    | 20.1    | 19.3     | 22.8    |  |  |  |  |

| 50       | 22.8   | 22.9   | 22.8   | 22.5   | 22.0    | 21.2    | 20.3    | 19.4     | 22.9    |  |  |  |  |

| 20       | 23.6   | 23.5   | 23.3   | 23.1   | 22.6    | 21.9    | 20.9    | 20.0     | 23.6    |  |  |  |  |

| 16       | 23.7   | 23.6   | 23.4   | 23.2   | 22.7    | 22.1    | 21.1    | 20.2     | 23.6    |  |  |  |  |

| 10       | 24.0   | 23.9   | 23.8   | 23.7   | 23.0    | 22.4    | 21.5    | 20.6     | 24.0    |  |  |  |  |

| 5        | 24.4   | 24.5   | 24.3   | 24.0   | 23.6    | 22.9    | 22.0    | 21.1     | 24.4    |  |  |  |  |

| 2.5      | 24.8   | 24.8   | 24.6   | 24.4   | 24.0    | 23.3    | 22.4    | 21.5     | 24.8    |  |  |  |  |

|          |        |        |        |        | SINC5   |         |         |          |         |

|----------|--------|--------|--------|--------|---------|---------|---------|----------|---------|

| ODR (Hz) | GAIN=1 | GAIN=2 | GAIN=4 | GAIN=8 | GAIN=16 | GAIN=32 | GAIN=64 | GAIN=128 | PGA OFF |

| 8000     | 207    | 294    | 352    | 312    | 295     | 484     | 897     | 1799     | 290     |

| 4000     | 305    | 247    | 287    | 295    | 231     | 397     | 725     | 1410     | 284     |

| 2000     | 85     | 79     | 87     | 103    | 143     | 235     | 465     | 821      | 75      |

| 1000     | 49     | 47     | 64     | 65     | 573     | 159     | 303     | 477      | 47      |

| 800      | 43     | 42     | 49     | 71     | 84      | 131     | 279     | 492      | 45      |

| 400      | 41     | 34     | 45     | 51     | 68      | 125     | 207     | 384      | 38      |

| 200      | 27     | 32     | 26     | 33     | 53      | 81      | 147     | 299      | 23      |

| 100      | 18     | 18     | 20     | 24     | 40      | 56      | 113     | 195      | 18      |

| 60       | 14     | 14     | 14     | 20     | 25      | 40      | 88      | 169      | 15      |

| 50 🧹     | 14     | 13     | 16     | 18     | 25      | 43      | 82      | 144      | 12      |

| 20       | 7      | 8      | 10     | 11     | 16      | 25      | 52      | 97       | 8       |

| 16       | 7      | 8      | 8      | 12     | 14      | 25      | 45      | 82       | 7       |

| 10       | 6      | 6      | 7      | 8      | 11      | 20      | 33      | 64       | 5       |