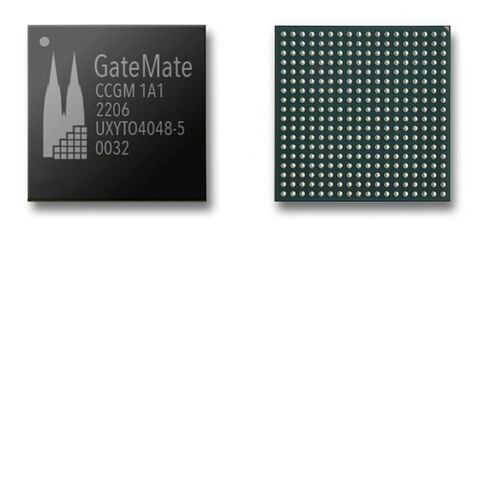

Main Features

GateMateTM FPGA Features

Novel CPE Architecture

- 20,480 programmable elements (CPE) for combinatorial and sequential logic

- 40,960 Latches / Flip-Flops within programmable elements

- CPE consists of LUT-tree with 8 inputs

- Each CPE configurable as 2-bit full-adder or 2x2-bit multiplier

Low Power Consumption

- GlobalfoundriesTM 28 nm SLP (Super Low Power) process

- 3 operation modes: low power, economy, speed

- No excessive start-up currents

- Only two supply voltages needed, can be applied in any order

Features

- 4 programmable PLLs

- Fast configuration with quad SPI interface up to 100 MHz

- Multi-Chip configuration

- 1,280 Kbit dual ported block RAM with variable data widths in 32 x 40 Kbit RAM cells

- Multipliers with arbitrary size implementable in CPE array

- Multiple clocking schemas

- All 162 GPIOs configurable as single-ended or LVDS differential pairs

- Double data rate (DDR) support in all GPIO cells

- 5 Gb/s SerDes

Package

- 324-ball BGA package (15x15 mm)

- Only 2 signal layers required on PCB